Проектирование цифрового устройства

ФБГОУ ВПО «Чувашский государственный

университет им. И.Н. Ульянова»

Кафедра информатики и вычислительной

техники

Пояснительная записка к курсовому

проекту

Дисциплина: Электротехника и

электроника

Тема: Проектирование цифрового

устройства

Выполнил:

ст. гр. ИВТ 21-10

Васильев И.С.

Руководитель:

Андреева А.А.

Чебоксары, 2012

ОГЛАВЛЕНИЕ

1. ЗАДАНИЕ НА ПРОЕКТИРОВАНИЕ

ЦИФРОВОГО УСТРОЙСТВА

. АНАЛИЗ И ТЕОРЕТИЧЕСКАЯ

ЧАСТЬ ПРОЕКТИРОВАНИЯ ЦИФРОВОГО УСТРОЙСТВА

. ПРОЕКТИРОВАНИЕ

ОПЕРАЦИОННОГО БЛОКА

.1 Регистры

.2 Схема сравнения

.3 Схема вычисления

контрольного кода

.4 Схема вычисления поправки

.5 Структурная схема

операционного блока

.6 Описание операционного

блока

. ОБЩАЯ СХЕМА СТРОЕНИЯ

АВТОМАТА

. АЛГОРИТМ РАБОТЫ АВТОМАТА

. ОПРЕДЕЛЕНИЕ СЛОВА УПРАВЛЕНИЯ

. ТАБЛИЦА ПЕРЕХОДОВ СОСТОЯНИЙ

. ПРОЕКТИРОВАНИЕ УПРАВЛЯЮЩЕГО

УСТРОЙСТВА

.1 Триггер

.2 Дешифратор

.3 Мультиплексор

.4 Логические элементы

. СХЕМА УПРАВЛЯЮЩЕГО

УСТРОЙСТВА

. РЕЗУЛЬТАТ РАБОТЫ ЭМУЛЯТОРА

MICROCAP

ВЫВОДЫ

СПИСОК ЛИТЕРАТУРЫ

1. ЗАДАНИЕ НА ПРОЕКТИРОВАНИЕ ЦИФРОВОГО УСТРОЙСТВА

Цифровой автомат для контроля логической операции: модифицированный сдвиг

вправо. Контрольный код исходного числа находится сложением триад по mod 7.

2. АНАЛИЗ И ТЕОРЕТИЧЕСКАЯ ЧАСТЬ ПРОЕКТИРОВАНИЯ ЦИФРОВОГО УСТРОЙСТВА

Пусть

задано число

имеющее

контрольный код

имеющее

контрольный код

Обозначим

код числа

,

сдвинутый влево, через

,

сдвинутый влево, через

.

Соответствующим образом обозначим и контрольный код:

.

Соответствующим образом обозначим и контрольный код:

Сдвиг

влево двоичного числа эквивалентен умножению на два. Так как при сдвиге числа

происходит потеря некоторых его разрядов, можно предполагать, что контрольный

код сдвинутого числа изменится на величину

:

:

(1)

(1)

где

-

сдвинутый влево контрольный код.

-

сдвинутый влево контрольный код.

Величина

зависит

от значений

зависит

от значений

и

и

, которые

при сдвиге выходят за пределы разрядной сетки.

, которые

при сдвиге выходят за пределы разрядной сетки.

Если

при сдвиге n-разрядного числа старшая единица выйдет за пределы

разрядной сетки, то это эквивалентно вычитанию

единиц

из контрольного кода сдвинутого числа

единиц

из контрольного кода сдвинутого числа

.

.

Если

при сдвиге контрольного кода выходит за пределы разрядной сетки разряд

, то это

эквивалентно уменьшению контрольного кода на

, то это

эквивалентно уменьшению контрольного кода на

. Такую

потерю надо восстановить прибавлением к контрольному коду единицы.

. Такую

потерю надо восстановить прибавлением к контрольному коду единицы.

В

общем случае (1) принимает вид

В

результате значения поправок

для

контроля выполнения левого сдвига по модулю будут:

для

контроля выполнения левого сдвига по модулю будут:

Значение

поправки

можно

заменить ее дополнением до модуля.

можно

заменить ее дополнением до модуля.

3.

ПРОЕКТИРОВАНИЕ ОПЕРАЦИОННОГО БЛОКА

.1

Регистры

Микросхема

К155ИР13 (74198) - универсальный, восьмиразрядный, синхронный регистр сдвига.

Каждая операция продолжается в регистре не более 20 нс, поэтому он пригоден для

обслуживания скоростных процессоров и ЗУ как буферный накопитель байта.

Синхронную работу регистру обеспечивают специальные входы выбора режима S0 и

SS. В таблице указаны сочетания уровней на этих входах, позволяющие переводить

регистр в режимы: хранения (на входах S0 и S1 напряжения низкого уровня),

параллельной загрузки (на этих входах напряжения высокого уровня), сдвига влево

(S1-в, S0-н) и сдвига вправо (S1-н, SO-в).

Кроме

однотипных параллельных входов, у микросхемы К155ИР13 (74198), DO - D7, первый

и последний разряды регистра имеют дополнительные D-входы: DSR - для сдвига

вправо и DSL для сдвига влево. Состоянием входов SO и S1 определяется также

прием тактового перепада от входа С. На входы SO и S1 перепад от высокого

уровня к низкому можно подавать, когда на входе С присутствует напряжение

высокого уровня. При параллельной загрузке (S1-в, SO-в) слово, подготовленное

на входах DO-D7, появится на выходах QO - Q7 после прихода последующего

положительного перепада тактового импульса.

Сброс

у регистра К155ИР13(74198) - асинхронный; при подаче на вход R активного

напряжения низкого уровня на выходах QO - Q7 фиксируются низкие уровни. Регистр

К155ИР13 (74198) потребляет ток 116 мA тактовая частота его может превышать 25

МГц.

Таблица

1. Таблица истинности К155ИР13

|

Режимработы

|

Вход

|

Выход

|

|

C

|

R

|

S1

|

S2

|

DSR

|

DSL

|

Dn

|

Q0

|

Q1-Q6

|

Q7

|

|

Сброс

|

х

|

Н

|

х

|

х

|

х

|

х

|

х

|

Н

|

Н-Н

|

Н

|

|

Хранение

|

↑

|

В

|

Н

|

Н

|

х

|

х

|

х

|

q0

|

q1-q6

|

q7

|

|

Сдвиг влево

|

↑

|

В

|

Н

|

Н

|

х

|

В

|

х

|

q1

|

q2-q7

|

Н

|

|

↑

|

В

|

В

|

Н

|

х

|

В

|

х

|

q1

|

q2-q7

|

В

|

|

Сдвиг вправо

|

↑

|

В

|

Н

|

В

|

Н

|

х

|

х

|

Н

|

q0-q5

|

q6

|

|

↑

|

В

|

Н

|

В

|

В

|

х

|

х

|

В

|

q0-q5

|

q6

|

|

Параллельная нагрузка

|

↑

|

В

|

В

|

В

|

В

|

х

|

dn

|

d0

|

d1-d6

|

d7

|

3.2 Схема сравнения

Схема сравнения чисел реализована на 2-х 4-разрядных компаратора серии

К555СП1.

К555СП1 - микросхема для сравнения 4-разрядных двоичных чисел,

представленных в прямом коде.

Рисунок

2. К555СП1

Микросхема имеет средства для наращивания разрядности сравниваемых чисел.

При этом вывода Y>X, Y<X, Y=X микросхемы, производящей сравнение младших разрядов,

соединяются с соответствующими входами Y>X, Y<X, Y=X микросхемы, производящей сравнение

старших разрядов числа. На вход Y=X микросхемы производящей сравнение

самых младших разрядов должен быть подан высокий уровень напряжения.

Таблица

2. Таблица истинности К555СП1

3.3 Схема вычисления

контрольного кода

Для вычисления контрольного кода был спроектирован новый элемент на базе

сумматора К155ИМ3 - 4-разрядный быстродействующий сумматор. Условно-графическое

обозначение представлено на рисунке.

Рисунок

3. К155ИМ3

Новый элемент выполняет функцию сумматора по модулю 7. Операндами

являются 2 трехразрядных числа. Результат также является трехразрядным.

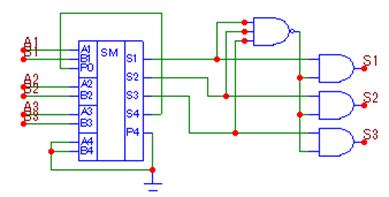

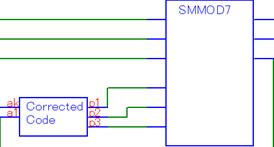

Рисунок

4. Сумматор по модулю 7 SMMOD7

В сумматоре используется один сумматор К155ИМ3. Для преобразования

значения «111» в «000» используется схема, реализованная на 3х элементах 2И и

на 1 элементе 3И-НЕ.

Рисунок

5. Схема сумматора SMMOD7

.4

Схема вычисления поправки

Для получения поправки к контрольному коду составлены карты Карно для

каждого разряда поправки. Карты Карно минимизированы и по ним составлена

комбинационная схема.

|

|

0

|

1

|

|

0

|

0

|

0

|

|

1

|

1

|

0

|

|

|

0

|

1

|

|

0

|

0

|

0

|

|

1

|

1

|

0

|

|

|

0

|

1

|

|

0

|

0

|

1

|

|

1

|

0

|

0

|

Рисунок

6. Схема вычисления поправки к контрольному коду

Вычисление скорректированного контрольного кода реализовано с помощью

схемы вычисления поправки и сумматора по модулю семь. Схема соединения

представлена на рисунке.

Рисунок

7. Схема вычисления скорректированного контрольного кода

3.5 Структурная

схема операционного блока

цифровой устройство арифметический триггер

Рисунок

8. Структурная схема операционного блока

.6

Описание операционного блока

· Операционный блок состоит из четырех регистров данных и

одного компаратора.

· Регистр RG1

хранит исходное число А.

· Регистр RG2

хранит результат сдвига B.

· Регистр RG3

хранит промежуточное значение контрольного кода исходного числа.

· Регистр RG4

хранит промежуточное значение контрольного кода результата.

· Компаратор CMP

сравнивает контрольные коды. С него в управляющее устройство подается сигнал

результата сравнения.

4. ОБЩАЯ СХЕМА СТРОЕНИЯ АВТОМАТА

5. АЛГОРИТМ РАБОТЫ АВТОМАТА

Рисунок

10. ГСА работы автомата

6. ОПРЕДЕЛЕНИЕ СЛОВА УПРАВЛЕНИЯ

Таблица

3. Таблица состояний автомата

|

|

RG1

|

RG2

|

RG3

|

RG4

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

000

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

|

001

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

|

010

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

|

011

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

|

100

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

|

101

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

|

110

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

|

111

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

7. ТАБЛИЦА ПЕРЕХОДОВ СОСТОЯНИЙ

Таблица

4. Таблица переходов состояний автомата

|

P

|

|

|

|

|

0

|

000

|

00

|

000

|

|

1

|

000

|

00

|

000

|

|

0

|

001

|

01

|

010

|

|

1

|

001

|

01

|

010

|

|

0

|

010

|

01

|

011

|

|

1

|

010

|

01

|

011

|

|

0

|

011

|

01

|

100

|

|

1

|

011

|

01

|

100

|

|

0

|

100

|

01

|

101

|

|

1

|

100

|

01

|

101

|

|

0

|

101

|

01

|

110

|

|

1

|

101

|

01

|

110

|

|

0

|

110

|

01

|

101

|

|

1

|

110

|

01

|

111

|

|

0

|

111

|

11

|

011

|

|

1

|

111

|

11

|

000

|

|

Признак

|

|

|

Пуск

|

00

|

|

Не завершено

|

01

|

|

Сдвиг совершен неверно

|

10

|

|

Сдвиг совершен верно

|

11

|

8. МИНИМИЗАЦИЯ И РАЗЛОЖЕНИЕ ПО БАЗИСАМ

Таблица

5. Минимизация состояний автомата при помощи карт Карно

|

|

00

|

01

|

11

|

10

|

|

P

|

|

|

|

|

|

00

|

0

|

0

|

1

|

0

|

|

01

|

1

|

1

|

0

|

0

|

|

11

|

1

|

1

|

0

|

1

|

|

10

|

0

|

0

|

1

|

0

|

|

|

00

|

01

|

11

|

10

|

|

P

|

|

|

|

|

|

00

|

0

|

1

|

0

|

1

|

|

01

|

0

|

1

|

1

|

0

|

|

11

|

0

|

1

|

0

|

1

|

|

10

|

0

|

1

|

0

|

1

|

|

|

00

|

01

|

11

|

10

|

|

P

|

|

|

|

|

|

00

|

0

|

0

|

0

|

1

|

|

01

|

1

|

0

|

1

|

1

|

|

11

|

1

|

0

|

0

|

1

|

|

10

|

1

|

0

|

0

|

1

|

Таблица

6. Минимизация признаков автомата при помощи карт Карно

|

|

00

|

01

|

11

|

10

|

|

P

|

|

|

|

|

|

00

|

0

|

0

|

0

|

0

|

|

01

|

0

|

0

|

1

|

0

|

|

11

|

0

|

0

|

1

|

0

|

|

10

|

0

|

0

|

0

|

0

|

|

|

00

|

01

|

11

|

10

|

|

P

|

|

|

|

|

|

00

|

0

|

1

|

1

|

1

|

|

01

|

1

|

1

|

1

|

1

|

|

11

|

1

|

1

|

1

|

1

|

|

10

|

0

|

1

|

1

|

1

|

8. ПРОЕКТИРОВАНИЕ УПРАВЛЯЮЩЕГО УСТРОЙСТВА

.1 Триггер

К155ТМ8 - микросхема представляет собой четыре триггера D-типа с прямыми

и инверсными выходами и предназначена для создания устройств памяти ЭВМ и

цифровой автоматики широкого применения. Отличительная особенность микросхемы -

наличие общих для всех триггеров входа синхронизации C и входа сброса R. Тактирование осуществляется фронтом

синхросигнала C, а установка выходов триггеров в состояние “0” - низким уровнем

напряжения на входе R. Условно-графическое обозначение представлено на рисунке

23.

Рисунок

11. К155ТМ8

Таблица

7. Таблица истинности К155ТМ8

|

Входы

|

Выход

|

|

R

|

C

|

D

|

Q

|

|

0

|

X

|

X

|

0

|

|

1

|

0/1

|

1

|

1

|

|

1

|

0/1

|

0

|

0

|

|

1

|

0

|

X

|

Q0

|

0 - предшествующее состояние триггера.

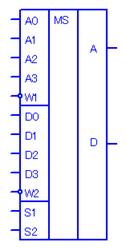

8.2 Дешифратор

Дешифратор двоичного кода 3-8 (К555ИД7).

К555ИД7 - дешифратор - демультиплексор 3-8. При выполнении микросхемой

функции дешифрации четырех разрядного двоичного кода, задаваемого на входах D0-D2, входы С1-С3 играют роль стробирующих, и на них должно быть

подано напряжение низкого (C2, C3) и высокого (C1) уровня. Условно-графическое

обозначение представлено на рисунке.

Рисунок

12. К555ИД7

Таблица

8. Таблица истинности К555ИД7

8.3 Мультиплексор

К555КП12 - микросхема представляет собой сдвоенный селектор-мультиплексор

1 из 4 с общими входами управления третьим состоянием. Наличие третьего

состояния на выходах позволяет использовать микросхему в системах с шинной

организацией обмена информации. Выход микросхемы переводится в высокоимпедансное

состояние при высоком уровне напряжения на соответствующем входе управления.

Условно-графическое обозначение представлено на рисунке.

Рисунок

13. К555КП12

Таблица 12. Таблица истинности

8.4 Логические элементы

К155ЛН1 -

инвертор

К155ЛН1 -

инвертор

Рисунок

14. К155ЛН1

К155ЛИ1 - элемент 2И

К155ЛЛ1 - элемент 2ИЛИ

9. СХЕМА

УПРАВЛЯЮЩЕГО УСТРОЙСТВА

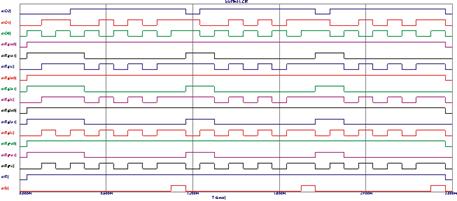

10. РЕЗУЛЬТАТ РАБОТЫ ЭМУЛЯТОРА MICROCAP

ВЫВОДЫ

В результате проделанной работы было разработано цифровое устройство для

контроля арифметической операции сдвига влево с вычислением контрольного кода

по модулю 7, которое включает в себя операционный блок и управляющее

устройство.

С помощью схемного эмулятора (использован программный пакет Micro-Cap) смоделировано управляющее устройство.

В проекте были использованы интегральные микросхемы отечественной серии

155 и 555.

Для реализации автомата были использованы следующие микросхемы:

Таблица

9. Список использованных микросхем

|

Наименование

|

Модель

|

Количество

|

|

8-разрядный сдвиговый

регистр

|

К155ИР13

|

4

|

|

4-разрядный цифровой

компаратор

|

К555СП1

|

1

|

|

Счетверенный D-триггер

со сбросом

|

К155ТМ8

|

1

|

|

Сдвоенный мультиплексор

|

К555КП12

|

1

|

|

Декодер 3 в 8

|

К555ИД7

|

1

|

|

Логический элемент НЕ

|

К155ЛН1

|

9

|

|

Логический элемент 2И

|

К155ЛИ1

|

22

|

|

Логические элемент 2ИЛИ

|

К155ЛЛ1

|

10

|

|

Логический элемент 3И-НЕ

|

К155ЛА4

|

1

|

|

4-разрядный сумматор

|

К155ИМ3

|

3

|

СПИСОК ЛИТЕРАТУРЫ

1. Савельев

А. Я. Основы информатики Учеб. для вузов. М.: Изд-во МГТУ им. Н.Э. Баумана,

2001. - 328 с.

. Амелина

М.А., Амелин С.А. Программа Схемотехнического Моделирования Microcap. М.:

горячая линия - телеком, 2007. - 466 с.