Проектирование функциональной ячейки вычислительного модуля в блоке цифровой обработки сигналов

СОДЕРЖАНИЕ

ВВЕДЕНИЕ

. СПЕЦИАЛЬНАЯ

ЧАСТЬ

.1 Требования

к вычислительному модулю

.2 Разработка

функциональной схемы ячейки

.3 Разработка

принципиальной электрической схемы ячейки

.3.1 Выбор

элементной базы

.3.2 Описание

электрической принципиальной схемы

.4 Расчет

тока потребления ФЯ вычислительного модуля

.5 Разработка

программного обеспечения дешифратора

.6 Разработка

программы для тестирования устройства

.

КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКАЯ ЧАСТЬ

.1 Разработка

ТЗ на конструкцию ФЯ вычислительного модуля для устройства цифровой обработки

сигналов

.2

Конструкторско-технологический анализ элементной базы ФЯ ячейки вычислительного

модуля

.3 Выбор

способа охлаждения ФЯ вычислительного модуля

.4 Выбор

компоновочной схемы и несущих конструкций ФЯ вычислительного модуля

.5 Разработка

конструкции ФЯ вычислительного модуля

.5.1 Расчет

площади печатной платы

.5.2

Разработка конструкции печатной платы

.6 Расчет

надежности по внезапным отказам ФЯ вычислительного модуля

.7 Расчет

вибропрочности конструкции ФЯ вычислительного модуля

.8 Оценка

технологичности конструкции ФЯ вычислительного модуля

.9

Технологический процесс сборки и монтажа ФЯ вычислительного модуля

2.10

Разработка специальной технологической оснастки

3.

ЭКОНОМИЧЕСКАЯ ЧАСТЬ

.1

Обоснование целесообразности разработки ячейки вычислительного модуля

.2

Определение трудоемкости и планирование разработки

.3

Определение затрат, себестоимости и цены ОКР

.4

Определение себестоимости и цены новой техники

.5

Определение затрат на эксплуатацию новой техники

.6

Определение и оценка показателей экономической эффективности разработки

. ОХРАНА

ТРУДА И ОКРУЖАЮЩЕЙ СРЕДЫ

.1 Анализ

условий труда разработчика

.1.1

Микроклимат

.1.2 Расчет

показателей теплового состояния человека

.1.3

Электрический ток (повышенное напряжение)

.2 Разработка

мероприятий по уменьшению отрицательного воздействия неблагоприятного

микроклимата и защите от воздействия электрического тока (повышенного

напряжения)

ЗАКЛЮЧЕНИЕ

СПИСОК

ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ

ПРИЛОЖЕНИЯ

ВВЕДЕНИЕ

Цифровая обработка сигналов является одной из наиболее быстро

развивающихся областей техники, обеспечивающих общий прогресс радиолокации в

последнее время.

Переход к многофункциональным РЛС диктуют повышенные требования к

многорежимности и универсальности используемых устройств обработки сигналов

[1]. В подобных РЛС устройство обработки сигналов (УОС) обеспечивает прием и

обработку в реальном масштабе времени радиолокационных сигналов, отраженных от

целей, и предназначено для обеспечения следующих основных режимов работы РЛС:

· обнаружение целей;

· сопровождение целей.

Упрощенная структурная схема РЛС представлена на рисунке 1.

Рисунок 1 - Упрощенная структурная схема РЛС

Передатчик РЛС вырабатывает сигнал, который попадает в приемо-передающую

антенну и излучается. Сигнал отражается от цели и воспринимается

приемо-передающей антенной. Далее принимаемый сигнал поступает на СВЧ приемник,

где происходит пространственная селекция, усиление сигнала и понижение несущей

частоты до величин, удобных для дальнейшей обработки. Устройство обработки

сигналов (УОС) реализует следующие операции:

· оптимальная частотно-временная фильтрация сигналов;

· предварительное обнаружение полезных сигналов;

· измерение координат, соответствующих обнаруженным сигналам;

· вычисление сигналов ошибок по угловым координатам, дальности

и скорости для сопровождаемых целей.

Результаты обработки передаются в вычислительный комплекс, в задачи

которого входит сопровождение целей и управление всеми устройствами РЛС.

Устройство обработки сигналов состоит из несколько взаимосвязанных

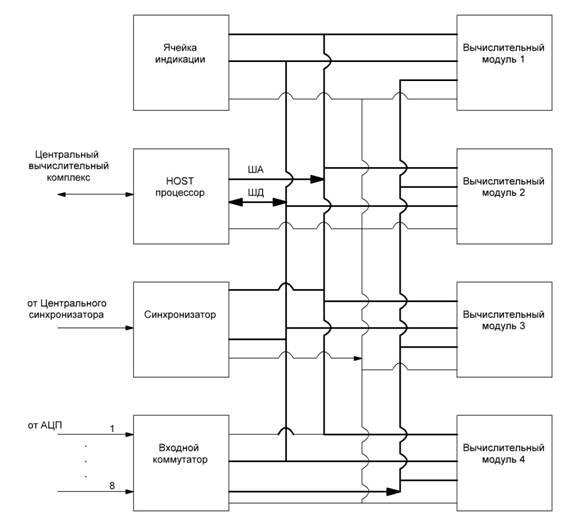

частей. Структурная схема УОС представлена на рисунке 2.

Рисунок 2 - Структурная схема УОС

Основными функциями первого блока являются управляемое усиление,

формирование полосы сигналов, обрабатываемых в цифровом виде, и

аналого-цифровое преобразование сигналов. После этого, сигналы поступают на

блок цифровой обработки сигналов через цифровой фильтр.

Блок цифровой обработки сигналов состоит из функциональных блоков

(ячеек): входной коммутатор, вычислительный модуль, устройство управления (Host

процессор), синхронизатор блока и ячейка индикации. Структурная схема блока

приведена на рисунке 3.

Входной информационный сигнал поступает от АЦП на входной коммутатор,

который распределяет информацию на четыре вычислительных модуля.

Вычислительные модули выполняют задачу обработки цифрового сигнала.

Рисунок 3 - Структурная схема блока ЦОС

Синхронизатор блока осуществляет общее тактирование ячеек. Тактирование

системы определяется режимом работы и глобальными тактовыми сигналами,

поступающими от центрального синхронизатора.

Устройство управления блока цифровой обработки сигналов выполняет

следующие функции:

) прием и обработка управляющей информации, поступающего по каналу

обмена от центрального вычислительного комплекса;

2) формирование и выдача управляющей информации для всех узлов

блока;

) прием результатов от вычислительных модулей и передача итоговой

информации в центральный вычислительный комплекс.

Ячейка индикации отображает состояние исправности/неисправности всех

узлов блока.

Функционирование блока происходит в режиме конвейера. Основные этапы:

· принятие входной информации;

· обработка информации;

· выдача обработанной информации.

В данном дипломном проекте рассматривается разработка ячейки

вычислительного модуля. Разрабатываемое устройство является одним из главных

звеньев в блоке цифровой обработки сигналов.

1.

СПЕЦИАЛЬНАЯ ЧАСТЬ

.1

Требования к вычислительному модулю

Устройство предназначено для осуществления обработки цифровых сигналов.

Напряжение питания ячейки 5В, потребляемый ток не более 7,5 А, тактовая частота

50 МГц.

Устройство должно обрабатывать информацию, поступающую от

аналого-цифрового преобразователя (АЦП), разрядность входных слов - 10.

Требования к конструкции ячейки вычислительного модуля приведены в ТЗ на

ее разработку.

1.2

Разработка функциональной схемы ячейки

Функциональная схема ячейки вычислительного модуля представлена в

Приложении А.

Функциональная схема ячейки состоит из следующих элементов:

) восемь процессорных элементов осуществляют обработку информации,

поступающей от АЦП через контроллер;

2) контроллер управления осуществляет распределение информации,

поступающей от АЦП по процессорам;

) дешифратор управляющих сигналов осуществляет преобразование

входных сигналов в определенные выходные для других элементов ячейки;

) буферы адреса, данных, сигналов управления, флагов, входной

информации, необходимые для корректной передачи сигналов;

) приемник высокоскоростной дифференциальной линии необходим для

обработки низкоуровневого дифференциального сигнала;

) источник тактовой частоты необходим для функционирования

процессоров и дешифратора.

На ячейку вычислительного модуля через входной коммутатор приходит

информация от АЦП, которую нужно обработать. В каждом слове, поступающем от

АЦП, десять разрядов, восемь из которых информационные, а два - служебные. Т.е.

на информационный вход контроллера непрерывно поступает по десятиразрядной

параллельной шине информация. Девятый и десятый разряды контроллер выделяет и

использует для своей работы, а разряды с первого по восьмой он распределяет по

четырехразрядной шине между процессорами в соответствующий момент времени. На

процессоры контроллер выдает информацию в следующем виде:

1-е слово содержит 31-28 разряды 32-х разрядного слова;

2-е слово содержит 27-24 разряды 32-х разрядного слова;

3-е слово содержит 23-20 разряды 32-х разрядного слова;

4-е слово содержит 19-16 разряды 32-х разрядного слова;

5-е слово содержит 15-12 разряды 32-х разрядного слова;

6-е слово содержит 11-8 разряды 32-х разрядного слова;

7-е слово содержит 7-4 разряды 32-х разрядного слова;

8-е слово содержит 3-0 разряды 32-х разрядного слова.

Все восемь процессоров получают от Host процессора по шинам адреса и данных

пакет управляющей информации, содержащий необходимые данные о выбранном способе

обработки информации, поступающей от АЦП через контроллер.

После обработки информации каждый процессор выставляет флаг о готовности

или неисправности, сигналы поступают на дешифратор, который обрабатывает их и

выставляет флаг готовности или неисправности для всех процессоров. Результат

обработки информации передается с процессоров по шине данных через дешифратор

на Host процессор. При необходимости, через Link-порты можно считать предварительные

результаты обработки информации. На дешифратор также поступают сигналы

управления, которые распределяются по элементам ячейки. Также дешифратор

управляет направлением передачи буфера данных между Host процессором и ячейкой

и выполняет функцию дешифрирования адреса.

1.3

Разработка принципиальной электрической схемы ячейки

.3.1 Выбор

элементной базы

Одним из важных вопросов обеспечения высоких характеристик ячейки

вычислительного модуля и блока цифровой обработки сигналов является выбор

элементной базы. При выборе элементной базы возможны два подхода:

· использование элементной базы, используемой ранее;

· использование новой перспективной элементной базы.

В первом случае отсутствует проблема освоения новых элементов, и процесс

разработки может быть ускорен, но характеристики устройства останутся прежними.

Во втором случае подход является прогрессивным, но более трудоемким.

Выбор новой элементной базы обуславливается также тем, что разработка

новой техники является длительным процессом, и необходимо обеспечить ее

передовой уровень на несколько лет вперед.

При выборе элементной базы ячейки вычислительного модуля необходимо

руководствоваться следующими критериями:

· обеспечение высокой производительности;

· возможность решения разноплановых задач;

· преемственность в других устройствах блока.

В данном дипломном проекте использована импортная элементная база. Выбор

зарубежной элементной базы обуславливается ее быстродействием, высокой

производительностью, надежностью, наличием полной документации на изделия и

эффективностью. По этим параметрам импортная элементная база намного

превосходит отечественную. Далее приведем краткое описание компонентов.

Процессорный элемент

Главным функциональным устройством ячейки вычислительного модуля является

процессорный элемент. В качестве процессорного элемента используем цифровой

сигнальный процессор ADSP TS201S семейства Tiger SHARC фирмы Analog Devices.

Также целесообразно использовать данный процессор для унификации элементов по

номенклатуре в блоке. Процессор ADSP-TS201S основан на статической

суперскалярной архитектуре, которая совмещает в себе функции архитектур RISC,

VLIW и стандартных цифровых сигнальных процессоров [2]. Аппаратная поддержка

типов данных с фиксированной и плавающей точкой в комбинации с передовыми

возможностями мультипроцессорной обработки позволяет процессору Tiger SHARC

обеспечивать непревзойденную производительность в операциях цифровой обработки

сигналов. Процессор обладает следующими характеристиками:

· тактовая частота до 600 МГц;

· производительность 1500 MFLOPs на Ватт;

· разрядность 64 бита;

· поддержка мультипроцессорных систем;

· операции с данными с плавающей и фиксированной запятой;

· возможность параллельного выполнения до четырех 32-разрядных

команд за один цикл;

· возможность отладки программного обеспечения на ячейке.

Процессор имеет двойной вычислительный блок, позволяющий реализовывать

набор SIMD инструкций (одиночный поток команд, множество потоков данных),

обеспечивающих параллелизм на уровне данных. Статическая суперскалярная

архитектура предоставляет возможность выполнять несколько математических

операций за один процессорный цикл (до четырёх инструкций за цикл). Другие

особенности процессора:

· время выполнения инструкции 1,67 нс;

· операции умножения могут производиться одновременно (до

восьми 16 битных операций умножения в формате с фиксированной запятой) и

реализуются посредством векторных вычислений;

· память организована в шесть блоков по 4 Мбит каждый, блок

содержит 128 килослов при 32 битах;

· четыре независимых 128-битных шины данных, каждая из которых

подключена к 4 мегабитным банкам памяти.

· поддерживается мультипроцессорный режим (до 8 процессоров).

Процессоры в таком режиме имеют общую шину, общее унифицированное

адресное пространство, возможность работы с другими мультипроцессорными

группами.

Начальная загрузка процессора может быть осуществлена одним из четырех

способов: загрузка из флэш-памяти (через внешний порт), Host загрузка (через

внешний процессор), загрузка через линк-порт и отсутствие начальной загрузки

(No boot). В нашем случае вид загрузки определяется комбинацией соединения

выводов процессора (strap mode pins). После этого процессор загружает программу

начальной загрузки, содержащей 256 слов стартовой информации.

Токи потребления:

ток потребления 0,05А при напряжении питания +1,05В;

ток потребления 0,25А при напряжении питания +1,5В;

ток потребления 0,15А при напряжении питания +2,5В.

Дешифратор

Дешифратор управляющих сигналов осуществляет преобразование входных

сигналов в определенные выходные для других элементов ячейки.

Для реализации дешифратора удобно использовать программируемые логические

интегральные схемы (ПЛИС). Такие микросхемы позволяют изменять функционал

устройства за счет изменения программного обеспечения, без изменения аппаратной

части.

В качестве микросхемы для реализации дешифратора выбираем микросхему

EPM7256 семейства MAX7000 фирмы Altera. Микросхема обладает следующими

основными характеристиками:

· количество логических вентилей - 5000;

· количество макроячеек - 256;

· число программируемых выводов - 164 [3].

Ток потребления равен 10,3мА при напряжении питания +3,3В.

Контроллер управления

Контроллер управления осуществляет распределение информации, поступающей

от аналого-цифрового преобразователя (АЦП) через входной коммутатор, по

процессорам.

Для реализации контроллера также используем ПЛИС. В качестве микросхемы

для реализации выбираем микросхему EP2C15A семейства Cyclone II фирмы Altera.

Основные характеристики микросхемы:

· количество логических ячеек - 14448;

· число программируемых выводов - 315 [4].

Токи потребления:

ток потребления 29мА при напряжении питания +1,2В;

ток потребления 61мА при напряжении питания +2,5В;

ток потребления 0,3мА при напряжении питания +3,3В.

Микросхема ПЗУ

Контроллер может быть сконфигурирован к загрузке из внешнего стираемого

программируемого ПЗУ. В качестве микросхемы памяти начального запуска и

программ выбираем микросхему EPCS16 фирмы Altera. Это 16-мегабитное устройство

флэш-памяти с тактовой частотой 40 МГц [5].

Ток потребления равен 15мА при напряжении питания +3,3В.

Приемник высокоскоростной дифференциальной линии

С разъема X1 на ячейку приходит LVDS сигнал (низкоуровневый

дифференциальный сигнал). Для обработки этого сигнала используем микросхему

SN65LVDS2 фирмы Texas Instruments, которая является приемником высокоскоростной

дифференциальной линии.

Ток потребления равен 5,5мА при напряжении питания +3,3В [6].

Буфера адреса, данных, сигналов управления

Передача сигналов в ячейке вычислительного модуля осуществляется как от

одного вывода микросхемы к другим выводам, так и к разъемам других ячеек блока.

Чтобы обеспечить надежную передачу сигналов необходимо использовать специальные

шинные приемопередатчики, называемые буферными элементами.

Одной из таких микросхем является микросхема 74GTLPH1645 фирмы Texas

Instruments. 74GTLPH1645 является 16-ти битным шинным приемопередатчиком (или

двумя 8-ми битными), который реализует преобразование уровней сигналов GTLP-ТТЛ

и ТТЛ-GTLP [7]. В зависимости от сигнала на выводе DIR микросхемы информация

может передаваться от порта A к порту B, либо наоборот. Вывод OE микросхемы

необходим для включения/выключения шинного преобразователя и возможности

изоляции шины. Таблица истинности представлена в таблице 1.1.

Таблица 1.1

Таблица истинности микросхемы 74GTLPH1645

|

Выводы

|

Выход

|

Режим

|

|

|

DIR

|

|

|

|

H

|

X

|

Z

|

Изоляция шины

|

|

L

|

L

|

B - A

|

Передача информации

|

|

L

|

H

|

A - B

|

|

где: H = High - высокий уровень сигнала;= Low - низкий уровень сигнала;-

не имеет значения уровень сигнала;- высокий импеданс выключенного состояния.

Ток потребления равен 40мА при напряжении питания +3,3В.

Еще одна микросхема подобного функционала - 74LVTH16245A фирмы Texas

Instruments. Микросхема предназначена для асинхронной передачи информации между

двумя шинами данных [8]. Логические уровни вывода управления направлением

передачи (DIR) и вывод разрешения передачи  активируют восемь выводов B-порта

или A-порта. Микросхема передает данные из шины A в шину B, когда выводы

B-порта являются активированными, и из шины B в шину A, когда выводы A-порта

активированы. Таблица истинности представлена в таблице 1.2.

активируют восемь выводов B-порта

или A-порта. Микросхема передает данные из шины A в шину B, когда выводы

B-порта являются активированными, и из шины B в шину A, когда выводы A-порта

активированы. Таблица истинности представлена в таблице 1.2.

Таблица 1.2

Таблица истинности микросхемы 74LVTH16245A

|

Выводы контроля

|

Выходной канал

|

Режим

|

|

|

DIR

|

Порт A

|

Порт B

|

|

|

L

|

L

|

Задействован

|

Z

|

B - A

|

|

L

|

H

|

Z

|

Задействован

|

A - B

|

|

H

|

X

|

Z

|

Z

|

Изоляция шины

|

Ток потребления равен 5мА при напряжении питания +3,3В.

Формирователь тактовых импульсов

Для функционирования процессора и дешифратора необходима системная

тактовая частота. В качестве источника тактовой частоты используем кварцевый

резонатор GXO-7531 с током потребления 45мА и напряжением питания +3,3В,

выходной частотой 100 МГц [9]. Выходной сигнал источника через нагрузку поступает

на микросхему IDT74FCT3807 фирмы IDT, выполняющую функцию формирователя

тактовых импульсов 1-10 (clock driver). Ток потребления равен 15,5мА при

напряжении питания +3,3В [10]. Функциональная схема формирователя представлена

на рисунке 1.1.

Буфер флагов

В качестве буферного элемента для выходных флагов используем микросхему

74LVT244 фирмы Texas Instruments. Данная микросхема является восьмиразрядным

буфером и формирователем линии, предназначенной специально для низкоуровневых

сигналов +3,3В [11]. Ток потребления равен 8,6мА при напряжении питания +3,3В.

Рисунок 1.1 - Функциональная схема формирователя IDT74FCT3807

Таблица истинности микросхемы представлена в таблице 1.3.

Таблица 1.3

Таблица истинности микросхемы 74LVT244

|

Входы

|

Выходы данных

|

|

|

Входы данных

|

|

|

L

|

L

|

L

|

|

L

|

H

|

H

|

|

H

|

X

|

Z

|

Буфер JTAG

Для возможности программирования и отладки программы работы процессора

необходимо реализовать подключение через JTAG интерфейс. Для этого используем

буфер 74AVC16244 фирмы Philips Semiconductors.

Ток потребления равен 0,1А при напряжении питания +3,3В [12].

Функциональная схема буфера представлена рисунке 1.2.

Для возможности тестирования и отладки программы работы процессора помимо

реализации подключения через JTAG интерфейс, необходимо реализовать

тактирование процессоров.

Рисунок 1.2 - Функциональная схема буфера 74AVC16244

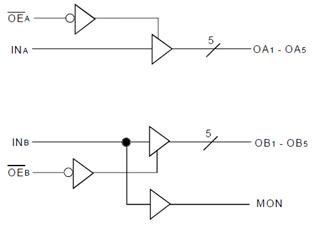

Для этого используем формирователь тактовых импульсов IDT49FCT3805E фирмы

IDT. Функциональная схема формирователя тактовых импульсов представлена на

рисунке 1.3 [13]. Устройство состоит из двух блоков формирователей, каждый из

которых состоит из пяти выходов, а также имеет вывод управления блоком.

Устройство предназначено для высокоскоростного распространения сигнала

тактирования, где качество сигнала является важным параметром.

Ток потребления равен 1,6мА при напряжении питания +3,3В.

Рисунок 1.3 - Функциональная схема формирователя IDT49FCT3805E

Преобразователи напряжения

Для функционирования всех элементов ячейки вычислительного модуля

необходимо обеспечить наличие следующих напряжений питания: +5В; +3,3В; +2,5В;

+1,5В; +1,2В; +1,05В. Напряжение питания ячейки +5В поступает из блока, а

остальные напряжения получим при помощи преобразователей напряжения.

Для получения напряжений +3,3В; +2,5В; +1,5В; +1,2В используем

преобразователь MAX1623 фирмы Maxim. Максимальный выходной ток для этой

микросхемы составляет 3А, погрешность выходного напряжения не превышает 1%,

коэффициент преобразования 95%, ток питания 0,4 мА [14].

В стандартном включении выходное напряжение микросхемы составляет +3,3В.

Для получения остальных значений напряжений необходимо использовать подключение

вывода FB (Feedback, обратная связь) через соответствующие резисторные делители

напряжения.

Для получения напряжения питания +1,05В используем микросхему PTH05060W

фирмы Texas Instruments. Максимальный выходной ток для этой микросхемы

составляет 10А, диапазон выходного напряжения от +0,8В до +3,6В [15].

Коэффициент преобразования напряжения для +1,05В составляет 86%, ток питания

0,4 мА.

.3.2

Описание электрической принципиальной схемы

Принципиальная электрическая схема представлена в Приложении Б. На первом

листе принципиальной электрической схемы представлены дешифратор (элемент D7);

буфер данных, состоящий из двух элементов (D3, D4); буфер адреса, состоящий из

двух элементов (D1, D2). С дешифратора через буфер флагов (D9) на Host

процессор передаются сигналы FLG1 и FLG2, где FLG1 - флаг готовности всех

процессоров, FLG2 - флаг неисправности процессоров. Буфер сигналов управления

состоит из двух элементов (D5, D6), управляющие сигналы (RD, START2, HBR, WR,

SEL1, SIGN1, SIGN2, RESET, SEL2, SOP2, SOP3, STOP) поступают на буфер

от Host процессора. Буфер управляющих сигналов соединен с дешифратором,

контроллером и процессорами.

Дешифратор осуществляет выдачу сигналов управления на процессоры (RDIN,

WRIN), сигналы прерывания на процессоры (IRQ0, IRQ1, IRQ2, IRQ3), сигналы

направления передачи буфера данных.

Буфер данных является двунаправленным и связывает Host процессор и ячейку вычислительного

модуля, шина данных соединена с процессорами (D15-D22) через дешифратор.

Сигналы на выводы микросхемы, определяющие направление передачи буфера данных

(M,  ), вырабатываются дешифратором, в

зависимости от значений сигналов HBG (разрешение передачи данных по шине),

SEL1IN (сигнал обращения Host

процессора ко всем ячейкам вычислительного модуля блока цифровой обработки

сигналов), RDINT (сигнал чтения).

), вырабатываются дешифратором, в

зависимости от значений сигналов HBG (разрешение передачи данных по шине),

SEL1IN (сигнал обращения Host

процессора ко всем ячейкам вычислительного модуля блока цифровой обработки

сигналов), RDINT (сигнал чтения).

Однонаправленная шина адреса соединена с несколькими элементами ячейки: с

дешифратором, с контроллером (D14), с процессорами.

Все информационные сигналы буферов данных и адреса поступают с разъема

X1.

На втором листе принципиальной электрической схемы представлен

контроллер, приемник высокоскоростной дифференциальной линии (D12), микросхема

ПЗУ (D10), а также буферный элемент (D13).

Устройство флэш-памяти предназначено для хранения программ контроллера.

Загрузка информации в микросхему ПЗУ осуществляется через разъем X5.

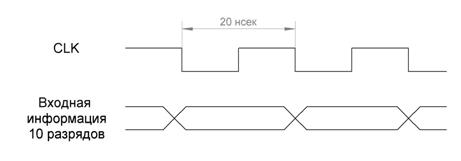

Информация с ячейки входного коммутатора поступает на контроллер через

буферный элемент с разъема X1. Временная диаграмма входной информации

представлена на рисунке 1.4.

Рисунок 1.4 - Временная диаграмма входной информации

Где CLK - тактовая частота.

В зависимости от работы блока цифровой обработки сигналов, информация

по-разному распределяется между процессорами. Распределение информации между

процессорами в общем случае представлено на рисунке 1.5.

Рисунок 1.5 - Распределение информации между процессорами в общем случае

Где LxDAT - данные, передаваемые x-процессору;- тактовая частота передачи

данных x-процессору.

Перед началом работы контроллера происходит его программирование.

Программирование контроллера осуществляет Host процессор. Диаграмма программирования контроллера

представлена на рисунке 1.6.

Рисунок 1.6 - Диаграмма программирования контроллера

В период времени между импульсами SIGN1 и признаком SIGN2 происходит программирование контроллера. На шине

AD00..AD02 Host процессор выставляет адрес, на шине

DI00..DI09 выставляет данные. Признак SIGN2 запускает контроллер на работу. Каждый раз между импульсом SIGN1 и признаком SIGN2 происходит программирование.

В каждом слове, поступающем от АЦП через входной коммутатор, десять

разрядов. Из них восемь разрядов - информационные, а два - служебные.

-е слово содержит 31-24 разряды 32-х разрядного слова;

-е слово содержит 23-16 разряды 32 разрядного слова;

-е слово содержит 15-8 разряды 32-х разрядного слова;

-е слово содержит 7-0 разряды 32-х разрядного слова.

Первое слово кроме информационных разрядов должно содержать в 9-м разряде

признак старшего байта (единица в 9-м разряде). Признак SIGN2 поступает на контроллер в составе

информации от входного коммутатора, он может прийти в десятом разряде любого

слова. Контроллер должен его выделить и начать работать, т.е. выдать на

процессоры информационные разряды по 4-х разрядной шине в соответствующий

момент времени.

Таким образом, получив от внешнего коммутатора одно 32-х разрядное слово

в виде четырех штук 8-ми разрядных слов, контроллер выдает на процессор восемь

штук 4-х разрядных слов. Сигналы на процессоры выдаются уровнями LVDS.

Для организации работы контроллера, на его вход приходит частота с

приемника высокоскоростной дифференциальной линии. После включения питания на

вход контроллера поступает сигнал сброса (RESETIN). На вход контроллера все

сигналы поступают уровнями ТТЛ (КМОП).

На 3-6 листах принципиальной электрической схемы представлены восемь

процессорных элементов.

Выбор рабочей частоты процессоров CCLK (core clock) определяется

подключением выводов SCLKRAT(2-0) в соответствии с таблицей 1.4.

Таблица 1.4

Определение множителя частоты CCLK процессора

|

SCLKRAT(2-0)

|

Множитель n

|

|

000 001 010 011 100 101 110

111

|

4 5 6 7 8 10 12 reserved

|

Рабочая частота процессора равна произведение выбранного множителя на

величину подключаемой входной системной частоты SCLK, т.е. n ×

SCLK. В данном дипломном

проекте выбрана рабочая частота процессора равная 250 МГц, т.е. комбинация 001

на выводах SCLKRAT при частоте SCLK равной 50 МГц.

Данные для обработки с контроллера поступают на Link-порты процессоров. Link-порты обеспечивают

возможность загрузки и передачи в процессор данных для обработки на фоне

решения процессором других задач. Каждый из 4-х дуплексных Link-портов имеет 4 передающих и 4

приемных каналов. Рассмотрим сигналы управления Link-портом.

Для передатчика:

выводы CLKOP и CLKON - выходы тактового сигнала;

вывод ACKI - вход сигнала установления связи за

контролем потока данных;

выводы DO3-0 - шина выходных данных.

Для приемника:

выводы CLKINP и CLKINN - входы принимающего тактового сигнала;

вывод ACKO - выход сигнала установления связи за

контролем потока данных;

выводы DI3-0 - шина входных данных.

Результат предварительной обработки данных процессорами поступает с Link-портов 1, 2, 3 первого процессора на

разъем X2.

Сигнал RESETIN - сигнал сброса, устанавливает процессор в начальное состояние,

подается на вывод  .

.

Вывод  - вход сигнала сброса по включению питания для внутренней

динамической памяти. Вывод

- вход сигнала сброса по включению питания для внутренней

динамической памяти. Вывод  необходимо подключить к выводу

необходимо подключить к выводу  .

.

Выводы  - входы сигналов прерываний. Если на процессор приходит один

из сигналов прерываний, то он начинает его отработку.

- входы сигналов прерываний. Если на процессор приходит один

из сигналов прерываний, то он начинает его отработку.

Выводы FLAG3-0 - выводы сигналов FLAG (флаг). Сигнал с вывода FLAG0 -

сигнал готовности процессора, сигнал с вывода FLAG1 - сигнал неисправности

процессора. Эти сигналы поступают на дешифратор. Выводы FLAG2-3

сконфигурированы для программных условий процессора.

Выводы ID2-0 - определяют ID (номер) каждого процессора в

многопроцессорной системе. Номера процессоров являются неизменными, и

присваиваются каждому процессору на этапе проектирования устройства.

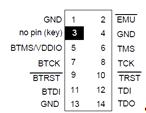

Выводы TCK, TMS, TDI, TDO,  ,

,  - выводы сигналов JTAG интерфейса,

необходимые для отладки программы работы процессора. Вывод TCK - вход тестового

тактового сигнала, поступающего с формирователя тестовых тактовых импульсов

(D29). Вывод TMS - вход сигнала выбора режима тестирования, вывод

- выводы сигналов JTAG интерфейса,

необходимые для отладки программы работы процессора. Вывод TCK - вход тестового

тактового сигнала, поступающего с формирователя тестовых тактовых импульсов

(D29). Вывод TMS - вход сигнала выбора режима тестирования, вывод  - вход сигнала тестового сброса, на

вывод TDI поступают входные тестовые данные. Сигналы на эти выводы поступают с

буфера JTAG (D30). С вывода TDO передаются выходные тестовые данные, с вывода

- вход сигнала тестового сброса, на

вывод TDI поступают входные тестовые данные. Сигналы на эти выводы поступают с

буфера JTAG (D30). С вывода TDO передаются выходные тестовые данные, с вывода  - сигнал эмуляции. Сигналы с выводов

TDO,

- сигнал эмуляции. Сигналы с выводов

TDO,  поступают на буфер JTAG.

поступают на буфер JTAG.

Выводы  - выводы, необходимые процессорам в многопроцессорной

системе для запроса доступа к шине и владению ей. Каждый процессор запускает

свою собственную

- выводы, необходимые процессорам в многопроцессорной

системе для запроса доступа к шине и владению ей. Каждый процессор запускает

свою собственную  -линию (соответствующую значению его ID2-0 входам) и

контролирует все другие. По сигналу

-линию (соответствующую значению его ID2-0 входам) и

контролирует все другие. По сигналу  определяется, какой из восьми

процессоров имеет доступ к шине данных.

определяется, какой из восьми

процессоров имеет доступ к шине данных.

Вывод  - вход сигнала блокировки. Выставляется Host процессором при возникновении

блокировки (безвыходного положения). Ситуация может случаться, когда Host процессор и сигнальный процессор

пытаются считать информацию одновременно из одной шины. В таком случае Host процессор подает сигнал на вывод

- вход сигнала блокировки. Выставляется Host процессором при возникновении

блокировки (безвыходного положения). Ситуация может случаться, когда Host процессор и сигнальный процессор

пытаются считать информацию одновременно из одной шины. В таком случае Host процессор подает сигнал на вывод  , тем самым принуждая сигнальный

процессор освободить шину до завершения невыполненной передачи данных. В данном

дипломном проекте сигнал на вывод

, тем самым принуждая сигнальный

процессор освободить шину до завершения невыполненной передачи данных. В данном

дипломном проекте сигнал на вывод  подается не с Host процессора, высокий уровень сигнала

на выводе реализован схемотехнически.

подается не с Host процессора, высокий уровень сигнала

на выводе реализован схемотехнически.

Выводы  - входы сигнала запроса прямого доступа к памяти. Высокий

уровень сигнала на выводах

- входы сигнала запроса прямого доступа к памяти. Высокий

уровень сигнала на выводах  , также как и на выводе

, также как и на выводе  реализован схемотехнически. Тем

самым разрешая Host процессору

прямой доступ к памяти сигнального процессора по инициализированным каналам.

реализован схемотехнически. Тем

самым разрешая Host процессору

прямой доступ к памяти сигнального процессора по инициализированным каналам.

Сигнал HBRIN - сигнал запроса Host процессора для работы с памятью процессора (для процессора), или запрос

на передачу данных (для шинных приемо-передатчиков). Сигнал HBG - ответ на

запрос.

Выводы  и

и  - соответственно входы сигналов чтения и записи. По сигналу

чтения происходит считывание информации из памяти процессора, по сигналу записи

происходит запись информации в память процессора.

- соответственно входы сигналов чтения и записи. По сигналу

чтения происходит считывание информации из памяти процессора, по сигналу записи

происходит запись информации в память процессора.

Вывод ACK - вход/выход сигнала подтверждения приема информации. Процессор

может убрать сигнал на выводе ACK, добавляя в состояния ожидания запросы

доступа к чтению и записи своей внутренней памяти.

Все не используемые выводы процессоров соединены по рекомендуемым

фирмой-производителем Analog Devices схемам.

На седьмом листе принципиальной электрической схемы представлены

преобразователи напряжения (D24, D25, D26, D31, D32, D33), источник тактовой

частоты (D23), формирователь тактовых импульсов (D27), а также микросхемы для

возможности программирования и отладки программы работы процессора: буфер JTAG

(D30) и формирователь тестовых тактовых импульсов (D29).

Возможность отладки рабочих программ реализована с помощью JTAG

интерфейса. Подключение процессоров к внешнему компьютеру по JTAG интерфейсу

осуществляется через стандартный 14-ти контактный разъем X6, представленный на

рисунке 1.7.

Рисунок 1.7 - 14-ти контактный JTAG разъем

Выводы разъем X6 соединены с соответствующими выводами процессоров через

буфер JTAG.

Формирователь тактовых импульсов обеспечивает тактирование процессоров и

дешифратора.

Рассмотрим схемы преобразователей напряжения.

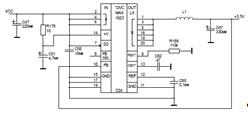

Напряжения питания +3,3В, +2,5В, +1,5В, +1,2В формируются на микросхемах

MAX1623. При стандартной схеме включения, которая представлена на рисунке 1.8,

выходное напряжение равно +3,3В.

Рисунок 1.8 - Стандартная схема включения микросхемы MAX1623

Для получения необходимого выходного напряжения необходимо организовать

обратную связь через делитель напряжения. Обратная связь подключается к выводу FB микросхемы. Схема включения

микросхемы с обратной связью представлена на рисунке 1.9.

Рисунок 1.9 - Схема включения микросхемы MAX1623 с обратной связью

В соответствие с документацией на микросхему для каждого номинала

выходного напряжения выбираем значения сопротивлений Rs1 и Rs2, в

данном случае R193 = 909 Ом и R194 = 10кОм.

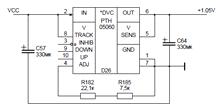

Напряжение питания +1,05В формируется на микросхемах PTH05060W.

Микросхема преобразует напряжение +5В в напряжение от +0,8В до +3,6В, в

зависимости от номинала резистора Rset в стандартной схеме включения микросхемы, которая представлена на

рисунке 1.10.

Рисунок 1.10 - Стандартная схема включения микросхемы PTH05060W

На рисунке 1.10 Rset =

R182 + R185.

В соответствие с документацией на микросхему рассчитаем Rset для выходного напряжения +1,05В:

Таким образом:

На последнем листе принципиальной электрической схемы расположены

развязывающие конденсаторы для каждого напряжения питания.

1.4 Расчет

тока потребления ФЯ вычислительного модуля

Для того, чтобы рассчитать ток потребления ФЯ вычислительного

модуля необходимо, для каждого номинала питания (VCC; +3,3В; +2,5В; +1,5В; +1,2В; +1,05) просуммировать

потребляемый ток по всем элементам. Далее необходимо учесть коэффициент

преобразования напряжения для каждого номинала относительно VCC (+5В). Таким образом, потребляемый

ток ФЯ вычислительного модуля рассчитывается по формуле:

где: IpowΣx - суммарный потребляемый ток для

каждого номинала питания;

ηx - коэффициент преобразования для каждого номинала

питания.

Суммарный потребляемый ток для каждого номинала питания равняется:

где: ni - количество микросхем с одинаковым

значением тока потребления;

Ii - ток, потребляемый i-й

микросхемой.

Согласно перечню элементов, представленному в Приложении В, следует

распределить микросхемы по группам с соответствующими номиналами напряжений.

· VCC: D24, D25, D26, D31, D32, D33;

· +3,3В: D1, D2, D3, D4, D5, D6, D7, D9, D10, D12, D13, D14, D23, D27, D29, D30;

· +2,5В: D14,

D15-D22;

· +1,5В: D15-D22;

· +1,2В: D14;

· +1,05В: D1-D5,

D15-D22.

Таким образом, потребляемый ток ФЯ вычислительного модуля равен:

Определим потребляемую мощность ФЯ по формуле:

где: I - потребляемый ток ФЯ;

U -

напряжение питания ФЯ.

Таким образом:

1.5

Разработка программного обеспечения дешифратора

Для разработки проекта ПЛИС дешифратора в данном дипломном проекте

используется САПР MAX+plus II фирмы Altera.

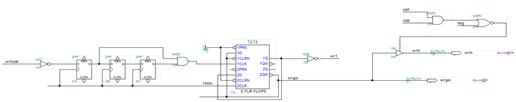

Графический файл проекта представлен на рисунках 1.11а, 1.11б, 1.11в,

1.11г.

На рисунке 1.11а изображен элемент DCVM1, все сигнальные входы микросхемы, а также выходные

сигналы микросхемы.

Вход input[4..1] представляет собой разряды

шины адреса AD26…AD29 процессора. Входы csb, csh, hbg, rdhost, wrhost

являются приемниками управляющих сигналов SEL2IN, SEL1IN, HBG, RDINT, WRINT соответственно. Сигнал SEL2IN -

сигнал обращения Host процессора к

ячейке вычислительного модуля, сигнал SEL1IN - сигнал обращения Host процессора ко всем ячейкам

вычислительного модуля блока цифровой обработки сигналов, сигнал HBG -

разрешение передачи данных по шине (ответ на HBR), сигнал RDINT - сигнал чтения информации из процессора,

сигнал WRINT - сигнал записи информации в память

процессора. Входы sop2, sop3, stop, signal1,

signal2 необходимы для формирования

сигналов прерывания для процессора. Входы fl01…fl08

являются входами сигналов готовности процессоров, входы fl11…fl18 - входы сигналов неисправности процессоров, вход flidc - вход сигнала от Host процессора. Вход 100m - вход сигнала тактовой частоты,

входы start и reset являются приемниками управляющих сигналов START и RESETIN соответственно.

Выход cskpi - выход сигнала обращения к контроллеру с дешифратора. Выход

mdan - выход сигнала управления шиной данных. Сигнал поступает на вывод DIR

микросхем буфера данных, в зависимости от уровня сигнала, буфер пропускает

данные либо от Host процессора на ячейку, либо наоборот. Таблица истинности

микросхемы представлена в таблице 1.1. Выходы irq0…irq3 - выходы сигналов

прерывания для процессоров. Выходы fl0, fl1 - выходы сигналов готовности и

неисправности для Host процессора соответственно, выход fl2 - выход сигнала

начала работы для процессоров.

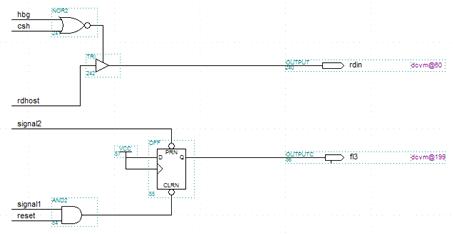

На рисунке 1.11б представлена реализация двунаправленной шины данных. На

рисунках 1.11в и 1.11г представлены схемы формирования сигналов чтения/записи

для процессоров (rdin/wrin), а также флага fl3.

Рисунок 1.11а - Графический файл проекта

Рисунок 1.11б - Графический файл проекта

Рисунок 1.11в - Графический файл проекта

Рисунок 1.11г - Графический файл проекта

Элемент DCVM1 представляет собой макромодель,

функционал которой реализован на языке VHDL. Текст программы представлен в Приложении Г.

Программа представляет собой процессы формирования выходных сигналов в

зависимости от уровня входных сигналов.

В начале программы происходит подключение всех необходимых библиотек, а

также описание входных и выходных портов. Далее, непосредственно, следует

описание процессов формирования выходных сигналов. Блок-схема алгоритма

программы макромодели DCVM1,

представлена на рисунке 1.12.

Рисунок 1.12 - Блок-схема алгоритма программы макромодели DCVM1

Процесс i1 формирует сигналы обращения к

контроллеру в зависимости от сигналов на входах input[4…1], а также от сигналов обращения Host процессора ко всем ячейкам

вычислительного модуля блока цифровой обработки сигналов или к определенной

ячейке в частности.

В зависимости от управляющих сигналов SOP2, STOP, SOP3, SIGN1 и SIGN2,

приходящих на дешифратор, в процессе i2 формируются сигналы прерываний для процессоров IRQ0, IRQ1, IRQ2 и IRQ3.

В процессах i3, i4, i5 формируются сигналы флагов FL0, FL1,FL2. Флаг FL0 - флаг готовности процессоров, он будет выставлен только в

том случае, если будут выставлены все флаги FL01…FL08

на процессорах, что соответствует их готовности. Флаг FL1 - флаг неисправности процессоров, он будет выставлен в том

случае, если выставлен, хотя бы один из флагов неисправности FL11…FL18 на процессорах.

В процессе m1 формируется

сигнал управления шиной данных. Управление шиной данных происходит двумя

сигналами - HBG и MDAN, которые поступают на выводы  и DIR буфера данных. Если Host процессор обращается к ячейкам вычислительного модуля

устройства цифровой обработки сигналов и разрешена передача данных по шине, а

также сигнал RDINT (вывод rdhost) равен нулю, т.е. происходит передача данных от ячейки

к Host процессору, то сигнал MDAN равен единице. При передаче данных

от ячейки к Host процессору сигнал MDAN равен нулю.

и DIR буфера данных. Если Host процессор обращается к ячейкам вычислительного модуля

устройства цифровой обработки сигналов и разрешена передача данных по шине, а

также сигнал RDINT (вывод rdhost) равен нулю, т.е. происходит передача данных от ячейки

к Host процессору, то сигнал MDAN равен единице. При передаче данных

от ячейки к Host процессору сигнал MDAN равен нулю.

Для моделирования работы дешифратора используем программный модуль MAX+plus II Simulator (симулятор). Симулятор MAX+plus II проверяет логические операции и внутренние временные

соотношения проекта, позволяет смоделировать работу проекта перед тем, как

запрограммировать его в микросхему [16]. Временные диаграммы проекта

представлены на рисунке 1.13.

Рисунок 1.13 - Временные диаграммы (начало)

Рисунок 1.13 - Временные диаграммы (окончание)

1.6 Разработка программы для тестирования устройства

Программа для тестирования устройства должна выполнять проверку отработки

всех прерываний процессором, а также выполнять проверку передачи информации по Link-порту. Блок-схема алгоритма тестовой

программы представлена на рисунке 1.14.

Сначала происходит инициализация работы процессора: устанавливается адрес

возврата из прерывания, разрешается кэш-память в каждом блоке памяти,

устанавливается рабочая частота. Далее необходимо установить вектора

прерываний: IRQ3, IRQ2, IRQ1, IRQ0. Для того чтобы программа имела

неограниченный доступ ко всем процессорным ресурсам, необходимо установить

режим супервизора процессора.

Перед тем как начать проверку отработки прерываний процессором,

необходимо произвести конфигурацию флагов FLAG0 и FLAG1

как выходных, где FLAG0 - флаг

готовности процессора, FLAG1

- флаг неисправности; флаги FLAG2

и FLAG3 - входы сигналов START и SIGN1/SIGN2

соответственно.

Далее начинается работа по подготовке процессора к отработке прерываний -

производится установка прерываний: разрешается IRQ3 (SIGN1/SIGN2) и выставляется запрет IRQ2 (SOP3), IRQ1 (STOP), IRQ0 (SOP2);

производится установка флагов: FLAG0=0,

FLAG1=0. Также необходимо провести

инициализацию Link-порта 0 на прием информации. После

чего процессор устанавливается в режим ожидания прерывания IRQ3.

По приходу на процессор сигнала прерывания IRQ3, начинается его обработка, осуществляется сброс всех

прерываний. Далее производится установка прерываний - разрешается IRQ0, а также анализ флага FLAG3. По значению сигнала FLAG3 определяется, какой сигнал пришел

на процессор - SIGN1 или SIGN2. Если FLAG3=0, то на процессор пришел сигнал SIGN1 - происходит установка флагов: FLAG0=1, FLAG1=0.

Рисунок 1.14 - Блок-схема алгоритма тестовой программы (начало)

Рисунок 1.14 - Блок-схема алгоритма тестовой программы (окончание)

Если FLAG3=1, то на процессор, соответственно,

пришел сигнал SIGN2 - происходит установка флагов: FLAG0=0; разрешается передача информации

по Link-порту 0; производится установка

прерываний - разрешается IRQ2 и

выставляется запрет IRQ3, IRQ0.

После обработки IRQ3

начинается обработка прерывания IRQ0,

осуществляется сброс всех прерываний. Далее производится установка прерываний -

разрешается IRQ2 и выставляется запрет IRQ3, IRQ0, а также установка флагов: FLAG0=1, FLAG1=0.

После этого выполняется проверка слова, записавшегося по Link0. Если слово записалось правильно -

происходит установка флагов: FLAG0=0.

Далее процессор переходит к отработке прерывания IRQ2, осуществляется сброс всех прерываний. Производится

установка прерываний - разрешается IRQ1 и выставляется запрет IRQ2,

а также установка флагов: FLAG0=0,

FLAG1=0. После чего процессор

устанавливается в режим ожидания прерывания IRQ1.

По приходу на процессор сигнала прерывания IRQ1, начинается его обработка, осуществляется сброс всех

прерываний. Далее производится установка прерываний - выставляется запрет IRQ1, а также установка флагов: FLAG0=1, FLAG1=1. Необходимо провести проверку записи информации в блоки

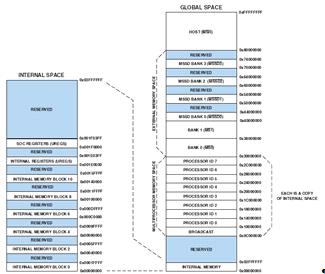

памяти процессора. Карта памяти процессора ADSP-TS201S представлена на рисунке 1.15. Для

проверки записи информации выбираются два адреса, соответствующие первому блоку

памяти (INTERNAL MEMORY BLOCK 0), и по ним происходит запись. Далее адреса изменяются

на адреса следующих блоков памяти, и по каждому из них происходит запись

информации. После того, как произведена запись в последний блок памяти (INTERNAL MEMORY BLOCK 10), тестовая программа прекращает свою работу.

Программа для тестирования устройства TESTPRC.asm

выполнена на языке Assembler в среде

программирования VisualDSP++ 4.5.

Рисунок 1.15 - Карта памяти процессора ADSP-TS201S

Текст программы представлен в Приложении Д.

Выводы:

В данной главе дипломного проекта:

· разработаны функциональная и принципиальная схемы ячейки вычислительного

модуля для блока цифровой обработки сигналов;

· выбрана соответствующая элементная база;

· выполнен расчет потребляемой мощности ФЯ;

· разработан проект ПЛИС дешифратора в САПР MAX+plus II фирмы Altera;

· разработана программа для тестирования устройства, которая

выполняет проверку отработки всех прерываний процессором, а также выполняет

проверку передачи информации по Link-порту.

Программа выполнена в среде программирования VisualDSP++ 4.5 на языке Assembler.

2.

КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКАЯ ЧАСТЬ

.1

Разработка ТЗ на конструкцию ФЯ вычислительного модуля для устройства цифровой

обработки сигналов

Технические требования.

) Состав изделия и требования к его конструкции.

Исходные данные:

Схема электрическая принципиальная (Э3) и перечень элементов (ПЭ3).

Базовая несущая конструкция:

габаритные размеры: 233,35×160 мм;

максимальная высота элементов на плате: не более 14,5 мм;

места установки разъемов определяются БНК;

установка планки: место установки планки определяется БНК, размер 261,8×20,2

мм или по ширине кратный

20,2 мм;

тип разъемов: вилка 02 01 160 2101, розетка угловая 617C037SAJ221, вилка PLD-10, вилка PLD-14;

число слоев МПП: не более 16;

класс точности МПП: 4.

) Требования к надежности.

Вероятность безотказной работы за 48 часов: 0,99.

Среднее время наработки до отказа должно быть не менее 6500 часов.

) Требования к уровню унификации и стандартизации.

Использование БНК

4) Требования к безопасности.

Изделие должно быть электробезопасно в условиях производства при

эксплуатации и обслуживании.

) Условия эксплуатации.

· группа аппаратуры 1.3;

· температура окружающей среды: минус 50 ºC

÷ 65 ºC;

· предельно высокая относительная влажность воздуха при

температуре 25 ºC - (95±3)%;

· давление: от 1,2·104 Па (90 мм рт. ст.);

· частота вибраций: 5 ÷ 25 Гц;

· ускорение при ударе: 98,1 м/с2 (10 g);

· длительность ударного ускорения: 5 ÷

10 мс;

· частота ударов: 40 ÷ 80 мин-1;

· ускорение вибраций: 19,62 м/с2 (2 g);

· принудительный обдув восходящим потоком воздуха t

= 15ºC.

2.2

Конструкторско-технологический анализ элементной базы ФЯ ячейки вычислительного

модуля

Микросхемы:

· 74GTLPH1645DGGR

- количество: 5;

- площадь микросхемы: 6,2 × 14,1 = 87,42 мм2;

- корпус: TSSOP (пластмассовый малогабаритный типа SO);

количество ножек: 56;

- температурный диапазон: от -40 до 85 ºC;

· SN74LVTH16245ADGG

- количество: 2;

- площадь микросхемы: 6,2 × 12,6 = 78,12 мм2;

- корпус: TSSOP;

- количество ножек: 48;

- температурный диапазон: от -40 до 85 ºC;

· EPM7256AEQI208-7

- количество: 1;

- площадь микросхемы: 30,6 × 30,6 =

936,36 мм2;

- корпус: PQFP

(пластмассовый корпус, ножки которого расположены по всем 4-м сторонам);

количество ножек: 208;

- температурный диапазон: от -40 до 85 ºC;

· 74LVT244MTC

- количество: 1;

- площадь микросхемы: 8,13 × 13,72 = 111,54 мм2;

- корпус: Ceramic Flatpacks (W) (керамический плоский корпус с

двухрядным расположением выводов);

количество ножек: 20;

- температурный диапазон: от -40 до 85 ºC;

· EPCS16SI8

- количество: 1;

- площадь микросхемы: 4,9 × 3,9 = 19,11 мм2;

- корпус: 8-SOIC;

- количество ножек: 8;

- температурный диапазон: от -40 до 85 ºC;

· SN65LVDS2DBV

- количество: 1;

- площадь микросхемы: 3 × 1,7 = 5,1 мм2;

- корпус: SOT23-5;

- количество ножек: 5;

- температурный диапазон: от -40 до 85 ºC;

· EP2C15AF484C6

- количество: 1;

- площадь микросхемы: 23 × 23 = 529 мм2;

- корпус: BGA;

- количество ножек: 484;

- температурный диапазон: от -40 до 85 ºC;

· ADSP-TS201SABP-050

- количество: 8;

- площадь микросхемы: 25 × 25 = 625 мм2;

- корпус: BGA;

- количество ножек: 576;

- температурный диапазон: от -40 до 85 ºC;

· GXO-7531/AIN-100.0 MHz

- количество: 1;

- площадь микросхемы: 5,2 × 7,2 = 37,44 мм2;

- корпус: керамический корпус с металлической крышкой;

количество ножек: 4;

- температурный диапазон: от -40 до 85 ºC;

· MAX1623EAP

- количество: 4;

- площадь микросхемы: 5,38 × 7,33 = 39,4 мм2;

- корпус: SSOP;

- количество ножек: 20;

- температурный диапазон: от -40 до 85 ºC;

· PTH05060WAH

- количество: 2;

- площадь микросхемы: 26,29 × 16,76 = 440,62 мм2;

- корпус: EUW (R-PDSS-T10);

- количество ножек: 10;

- температурный диапазон: от -40 до 85 ºC;

· IDT74FCT3807EPYI

- количество: 1;

- площадь микросхемы: 5,38 × 7,33 = 39,4 мм2;

- корпус: SSOP;

- количество ножек: 20;

- температурный диапазон: от -40 до 85 ºC;

· IDT49FCT3805EPYI

- количество: 1;

- площадь микросхемы: 5,38 × 7,33 = 39,4 мм2;

- корпус: SSOP;

- количество ножек: 20;

- температурный диапазон: от -40 до 85 ºC;

· 74AVC16244DGG

- количество: 1;

- площадь микросхемы: 6,2 × 12,6 = 78,12 мм2;

- корпус: SSOP;

- количество ножек: 48;

- температурный диапазон: от -40 до 85 ºC;

Резисторные сборки:

· EXB28V102JX

количество: 1;

- площадь: 2 × 1 = 2 мм2;

количество ножек: 8;

выводы/корпус: SMD;

температурный диапазон: от -55 до 125 ºC;

· EXB2HV103J

количество: 1;

- площадь: 3,8 × 1,6 = 6,08 мм2;

количество ножек: 16;

выводы/корпус: SMD;

температурный диапазон: от -55 до 125 ºC;

Разъемы:

· Розетка угловая 617С037SAJ221 (77SDC37SA4CH4FC309)

количество: 1;

- площадь, занимаемая на плате: 69,4 ×

12,3 = 853,62 мм2;

количество контактов: 37;

номинальный ток: 5А;

температурный диапазон: от -55 до 105 ºC;

· Вилка 02 01 160 2101

количество: 2;

- площадь, занимаемая на плате: 1354 мм2;

количество контактов: 160;

номинальный ток: 5А;

температурный диапазон: от -55 до 105 ºC;

· Вилка PLD-10

количество: 2;

- площадь, занимаемая на плате: 12,7 ×

5,08 = 64,52 мм2;

количество контактов: 10;

номинальный ток: 3А;

температурный диапазон: от -55 до 140 ºC;

· Вилка PLD-14

количество: 1;

- площадь, занимаемая на плате: 17,78 ×

5,08 = 90,32 мм2;

количество контактов: 14;

номинальный ток: 3А;

температурный диапазон: от -55 до 140 ºC;

Резисторы:

У всех резисторов Р1-12-0,125 одинаковый корпус SMD 0805:

количество элементов: 133;

- площадь: 2 × 1,25 = 2,5 мм2;

температурный диапазон: от -55 до 125 ºC;

Ферритовые бусинки:

· BDS3/3/4.6-4S2

количество: 8;

- площадь: 4,6 × 3 = 13,8 мм2;

выводы/корпус: SMD;

температурный диапазон: от -55 до 125 ºC;

Катушки индуктивности:

· SDR0805-4R7M

количество: 4;

- площадь: 3,14 × 3,92 = 47,78 мм2;

индуктивность: 4.7мкГн;

выводы/корпус: SDR

0805;

температурный диапазон: от -40 до 105 ºC;

Конденсаторы:

· Корпус SMD 0805

количество: 292;

- площадь: 2 × 1,25 = 2,5 мм2;

температурный диапазон: от -55 до 125 ºC;

· Корпус SMD 1206

количество: 6;

- площадь: 3,2 × 1,6 = 5,12 мм2;

температурный диапазон: от -55 до 125 ºC;

· Корпус

SMD 7343 TANTALUM

- количество: 55;

- площадь: 7,3 × 4,3 = 31,39 мм2;

температурный диапазон: от -55 до 125 ºC;

· Корпус

SMD 3216 TANTALUM

- количество: 4;

- площадь: 3,2 × 1,6 = 5,12 мм2;

температурный диапазон: от -55 до 125 ºC;

· Корпус SMD 0201

количество: 62;

- площадь: 0,6 × 0,3 = 0,18 мм2;

температурный диапазон: от -55 до 125 ºC;

· EEEFKJ101UAR 6.3 V-100 uF±20%

количество: 4;

- площадь: 3,14 × 2,52 = 19,63 мм2;

выводы/корпус: SMD;

температурный диапазон: от -55 до 105 ºC;

· EEEFK1C100AR 16 V-10 uF±20%

количество: 9;

- площадь: 3,14 × 22 = 12,56 мм2;

выводы/корпус: SMD;

температурный диапазон: от -55 до 125 ºC.

2.3 Выбор

способа охлаждения ФЯ вычислительного модуля

Массогабаритные характеристики РЭС в значительной мере зависят от способа

охлаждения, обеспечивающего нормальный тепловой режим изделия [17]. Поэтому

выбор системы охлаждения является одной из важнейших проектно-конструкторских

задач.

При выборе системы охлаждения используются следующие исходные данные:

· тепловой поток P, Вт,

рассеиваемый поверхностью теплообмена изделия;

· площадь поверхности теплообмена Sк, м2;

· допустимая рабочая температура наименее теплостойкого

элемента tэл min,

ºC;

· максимальная температура окружающей среды tс max,

ºC;

· минимальное давление окружающей среды Hс min, мм рт. ст.

Значение теплового потока приближенно определяют через потребляемую

мощность от источников питания мощность PП с учетом коэффициента полезного действия изделия η:

Т.к. ячейка вычислительного модуля цифровая, то η

= 0. Тогда P = 30,63 Вт.

Площадь поверхности теплообмена Sк = 2 × 0,23335 × 0,16 = 0,07467 м2; допустимая рабочая

температура наименее теплостойкого элемента tэл min

= 85ºC; максимальная

температура окружающей среды tс

max

= 65ºC; минимальное

давление окружающей среды Hс

min = 90 мм рт. ст.

Найдем поверхностную плотность теплового потока и допустимый перегрев в

конструкции:

где: kH - поправочный коэффициент на

давление окружающей среды;

H =

760 мм рт. ст. - нормальное давление.

Таким образом:

Значения POS и Δtдоп представляют собой координаты точки,

положение которой на диаграмме (рисунок 2.1) определяет систему охлаждения

конструкции.

Незаштрихованные зоны диаграммы относятся к следующим способам

охлаждения: 1 - естественное воздушное; 3 - принудительное воздушное; 5 -

принудительное жидкостное; 9 - принудительное испарительное.

Рисунок 2.1 - Диаграмма выбора способа охлаждения

Заштрихованным зонам соответствуют следующие способы охлаждения: 2 -

естественное и принудительное воздушное; 4 - принудительное воздушное и

жидкостное; 6 - принудительное жидкостное и естественное испарительное; 7 -

принудительное жидкостное, принудительное и естественное испарительное; 8 -

естественное и принудительное испарительное.

По диаграмме видно, что необходимо принудительное воздушное охлаждение.

Принудительное воздушное охлаждение обеспечивается в конструкции блока.

.4 Выбор

компоновочной схемы и несущих конструкций ФЯ вычислительного модуля

Выбор типа конструкции и компоновочного решения блока обуславливается

объектом установки РЭС, видом и интенсивностью воздействия дестабилизирующих

факторов.

Выбор компоновочной схемы блока проводится по результатам анализа

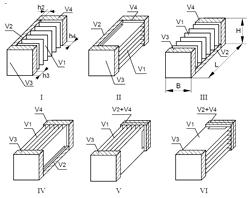

возможных вариантов организации его внутренней структуры (рисунок 2.2).

Рисунок 2.2 - Вариант организации структуры компоновочной схемы

Необходимо обеспечить принудительное воздушное охлаждение восходящим

потоком воздуха. Вариант I

компоновочной схемы предпочтительней при набегающем воздушном потоке снизу.

Также следует учесть конструкцию ФЯ. Исходя из этого выбираем I вариант конструкции блока.

2.5

Разработка конструкции ФЯ вычислительного модуля

.5.1

Расчет площади печатной платы

Разработка конструкции на корпусных ИС состоит в определении площади и

геометрических размеров печатной платы, проверке возможности размещения

радиоэлементов на плате, разработке конструкции печатной платы и определении

геометрических размеров ячейки.

Площадь печатной платы, необходимую для одностороннего размещения

радиоэлементов, находят по формуле:

где: qs - коэффициент дезинтеграции площади;

Sэл

i - установочная площадь i-го радиоэлемента;

n -

число элементов.

где: Sэл - площадь всех элементов на плате;

Sмикросхем - площадь всех микросхем на плате;

Sрезистор - площадь всех резисторов на плате;

Sконденсатор - площадь всех конденсаторов на

плате;

Sиндукт - площадь всех катушек индуктивности

на плате;

Sразъем - площадь всех разъемов на плате;проч

- площадь всех остальных элементов на плате.

Т.к. площадь всех резисторов одинаковая:

Принимаем qs = 2,

тогда:

Таким образом, выбираем размер платы 233,35×160 мм, заданный в ТЗ, т.к. он

удовлетворяет расчетным данным (233,35 × 160 = 37336 мм2 > 31122,2 мм2).

2.5.2

Разработка конструкции печатной платы

Класс точности многослойной печатной платы - 4, соответственно:

минимальная ширина проводников t, мм: 0,15 мм;

минимальное расстояние между проводниками s, мм: 0,15 мм;

гарантированная ширина пояска в наружном слое bН, мм: 0,05 мм;

гарантированная ширина пояска во внутреннем слое bВ, мм: 0,03 мм;

отношение диаметра металлизированного отверстия к толщине платы kДТ = 0,25 мм.

Материал платы - двухсторонний стеклотекстолит FR-4. Толщину многослойной печатной платы выбираем 1,74 мм

(число слоев: 16).

В результате выполнения конструкторско-технологических расчетов

определяют геометрические размеры элементов проводящего рисунка и их взаимного

расположения с учетом производственных погрешностей. Расчету подлежат диаметры

монтажных и переходных отверстий, значения ширины проводника и расстояния между

проводниками, диаметр контактной площадки.

Минимальный диаметр переходного отверстия:

где: kдт - отношение диаметра

металлизированного отверстия к толщине платы;

hпл - толщина печатной платы.

Примем диаметр переходного отверстия равный 0,9 мм.

Минимальный диаметр монтажного отверстия:

где: dв - диаметр вывода радиоэлемента, dв = 0,27 мм ;

Δ = 0,2…0,6 мм - зазор между поверхностью вывода

и поверхностью отверстия;

hг = 0,02…0,06 мм - толщина

гальванически осаждаемой меди;

δд = 0,012 мм - погрешность диаметра отверстия.

Примем диаметр монтажного отверстия равный 0,9 мм.

Минимальный диаметр контактной площадки:

где: bн - гарантированная ширина пояска в наружном слое;

δ0 = 0,07 мм - погрешность расположения отверстия;

δкп = 0,15 мм - погрешность расположения

контактной площадки;

δфф = 0,06 мм - погрешность фотокопии и

фотошаблона;

hф - толщина фольги на диэлектрическом

основании, hф = 0,035 мм для двухстороннего стеклотекстолита FR-4.

2.6 Расчет

надежности по внезапным отказам ФЯ вычислительного модуля

Оценочный расчет надежности заключается в определении показателей

надежности функциональной ячейки по известным характеристикам надежности

составляющих компонентов и условиям эксплуатации. Основными количественными

характеристиками надежности являются вероятность безотказной работы (ВБР) РЭС в

течение заданной наработки (0;t) (в данном случае рассчитывается ВБР для

нерезервированных систем):

где t - время непрерывной работы изделия;

и среднее время наработки до отказа:

где: t - время непрерывной работы ячейки;

λэ - эксплуатационное значение интенсивности отказов.

где: λэi

- эксплуатационное значение интенсивности отказов i-го элемента, учитывающее внешние воздействия, влияние

тепловых и электрических элементов;

n -

число элементов.

Расчет надежности проводим в программе «Автоматизированная система

расчета надежности (АСРН)».

Исходные данные:

расчет в режиме эксплуатации;

группа аппаратуры: 1,3;

температура окружающей среды, ºC: 55.

Данные расчета надежности представлены в таблице 2.1.

Таблица 2.1

Расчет суммарной интенсивности отказов входящих модулей и ЭРЭ

|

Тип ЭРЭ

|

Количество

|

λб (бсг)

|

λэ, 1/ч

|

λэ × n,

1/ч

|

|

Интегральные микросхемы

|

|

74GTLPH1645DGGR

|

5

|

-

|

0,96×10-7

|

4,8×10-7

|

|

SN74LVTH16245ADGG

|

2

|

-

|

0,83×10-7

|

1,66×10-7

|

|

EPM7256AEQI208-7

|

1

|

-

|

0,4×10-6

|

0,4×10-6

|

|

74LVT244MTC

|

1

|

-

|

0,92×10-8

|

0,92×10-8

|

|

EPCS16SI8

|

1

|

-

|

3,04×10-9

|

3,04×10-9

|

|

SN65LVDS2DBV

|

1

|

-

|

1,97×10-8

|

1,97×10-8

|

|

EP2C15AF484C6

|

1

|

-

|

2,74×10-7

|

2,74×10-7

|

|

ADSP-TS201S

|

8

|

-

|

1,77×10-6

|

1,416×10-5

|

|

GXO-7531/AIN-100.0 MHz

|

1

|

-

|

0,94×10-8

|

0,94×10-8

|

|

MAX1623EAP

|

4

|

-

|

0,84×10-7

|

3,36×10-7

|

|

PTH05060WAH

|

2

|

-

|

0,39×10-7

|

7,8×10-8

|

|

IDT74FCT3807EPYI

|

1

|

-

|

0,38×10-7

|

0,38×10-7

|

|

IDT49FCT3805EPYI

|

1

|

-

|

0,38×10-7

|

0,38×10-7

|

|

74AVC16244DGG

|

1

|

-

|

0,85×10-7

|

0,85×10-7

|

|

Резисторы

|

|

EXB28V102JX

|

1

|

0,37×10-8

|

0,83×10-9

|

0,83×10-9

|

|

EXB2HV103JV

|

1

|

0,37×10-8

|

1,23×10-8

|

1,23×10-8

|

|

Р1-12-0,125-33 Ом

|

3

|

0,37×10-8

|

2,77×10-9

|

8,31×10-9

|

|

Р1-12-0,125-100 Ом

|

1

|

0,37×10-8

|

3,1×10-9

|

3,1×10-9

|

|

Р1-12-0,125-1 кОм

|

1

|

0,37×10-8

|

3,1×10-9

|

3,1×10-9

|

|

Р1-12-0,125-4,75 кОм

|

71

|

0,37×10-8

|

3,1×10-9

|

2,201×10-7

|

|

Р1-12-0,125-0,15

Ом

|

18

|

0,37×10-8

|

3,1×10-9

|

5,58×10-8

|

|

Р1-12-0,125-470 Ом

|

8

|

0,37×10-8

|

3,1×10-9

|

2,48×10-8

|

|

Р1-12-0,125-2 кОм

|

1

|

0,37×10-8

|

3,1×10-9

|

3,1×10-9

|

|

Р1-12-0,125-2,55

кОм

|

1

|

0,37×10-8

|

3,1×10-9

|

3,1×10-9

|

|

Р1-12-0,125-221

Ом

|

4

|

0,37×10-8

|

3,1×10-9

|

1,24×10-8

|

|

Р1-12-0,125-274 Ом

|

4

|

0,37×10-8

|

3,1×10-9

|

1,24×10-8

|

|

Р1-12-0,125-10 Ом

|

4

|

0,37×10-8

|

2,77×10-9

|

1.108×10-8

|

|

Р1-12-0,125-22 кОм

|

2

|

0,37×10-8

|

3,1×10-9

|

6,2×10-9

|

|

Р1-12-0,125-10 кОм

|

6

|

0,37×10-8

|

2,77×10-9

|

1,662×10-8

|

|

Р1-12-0,125-7,5 кОм

|

2

|

0,37×10-8

|

3,1×10-9

|

6,2×10-9

|

|

Р1-12-0,125-110 кОм

|

4

|

0,37×10-8

|

3,1×10-9

|

1,24×10-8

|

|

Р1-12-0,125-900 Ом

|

1

|

0,37×10-8

|

2,77×10-9

|

2,77×10-9

|

|

Р1-12-0,125-3,6 кОм

|

1

|

0,37×10-8

|

2,77×10-9

|

2,77×10-9

|

|

Р1-12-0,125-13 кОм

|

1

|

0,37×10-8

|

2,77×10-9

|

2,77×10-9

|

|

Конденсаторы

|

|

SMD 0805-X7R 50 V-0.1 uF

|

91

|

2

×10-9

|

0,54

×10-8

|

4,91×10-7

|

|

SMD 0805-NP0 50 V-1000 pF

|

16

|

2

×10-9

|

2,52

×10-9

|

4,03×10-8

|

|

SMD 0805-X7R 50 V-1000 pF

|

64

|

2

×10-9

|

2,25

×10-9

|

1,44×10-7

|

|

SMD 0805-X7R 50 V-1 uF

|

13

|

2

×10-9

|

0,47

×10-8

|

6,11×10-8

|

|

SMD 1206-Y5V 16 V-10 uF

|

6

|

2

×10-9

|

0,52

×10-8

|

3,12×10-8

|

|

SMD 7343 TANTALUM-10 V-220

uF

|

4

|

0,5

×10-10

|

1,17

×10-10

|

4,68×10-10

|

|

SMD 3216 TANTALUM-16 V-4.7

uF

|

4

|

0,5

×10-10

|

0,48

×10-10

|

1,92×10-10

|

|

SMD 7343 TANTALUM-10 V-330

uF

|

8

|

0,5

×10-10

|

1,28

×10-10

|

1,02×10-9

|

|

SMD 0805-NP0 50 V-47 pF

|

4

|

2

×10-9

|

1,71

×10-9

|

6,84×10-9

|

|

SMD 7343 TANTALUM-16 V-100

uF

|

35

|

0,5

×10-10

|

0,97

×10-10

|

3,4×10-9

|

|

SMD 0805-X7R 50 V-0.01 uF

|

84

|

2

×10-9

|

2,77

×10-9

|

2,33×10-7

|

|

SMD 0201-X5R 10 V-0.01 uF

|

25

|

2

×10-9

|

0,44

×10-8

|

1,1×10-7

|

|

SMD 0201-X5R 16 V-1000 pF

|

26

|

2

×10-9

|

2,52

×10-9

|

6,55×10-8

|

|

SMD 0805-Y5V 10 V-2.2 uF

|

10

|

2

×10-9

|

0,71

×10-8

|

7,1×10-8

|

|

EEEFKJ101UAR 6.3 V-100 uF

|

4

|

1,2

×10-10

|

2,28

×10-9

|

9,12×10-9

|

|

SMD 7343 TANTALUM-25 V-33

uF

|

4

|

0,5

×10-10

|

0,76

×10-10

|

3,04×10-10

|

|

SMD 0201-X5R 6.3 V-0.1

uF±10%

|

11

|

2

×10-9

|

0,54

×10-8

|

5,94×10-8

|

|

EEEFK1C100AR 16 V-10 uF

|

9

|

1,2

×10-10

|

0,44

×10-9

|

3,96×10-9

|

|

SMD 0805-Y5V 10 V-4.7 uF

|

10

|

2

×10-9

|

0,62

×10-8

|

6,2×10-8

|

|

SMD 7343 TANTALUM-10 V-150

uF

|

4

|

0,5

×10-10

|

1,12

×10-10

|

4,48×10-10

|

|

Трансформаторы

|

|

BDS3/3/4.6-4S2

|

8

|

3

×10-11

|

0,57

×10-10

|

4,56×10-10

|

|

SDR0805-4R7M

|

4

|

3

×10-11

|

0,57

×10-10

|

2,28×10-10

|

|

Соединители

|

|

02 01 160 2101

|

2

|

0,46

×10-7

|

0,61

×10-6

|

1,22×10-6

|

|

Итого для эксплуатации

|

1,91

×10-5

|

|

617B037SAJ221

|

1

|

0,46

×10-7

|

0,61

×10-6

|

0,61

×10-6

|

|

PLD-10

|

2

|

0,46

×10-7

|

0,61

×10-6

|

1,22

×10-6

|

|

PLD-14

|

1

|

0,46

×10-7

|

0,61

×10-6

|

0,61

×10-6

|

|

Итого для контрольных

элементов

|

2,44

×10-6

|

|

Итого для модуля

|

2,15

×10-5

|

|

|

|

|

|

|

λэ = 2,15

×10-5 [1/ч] - эксплуатационное значение

интенсивности отказов для всего модуля, учитывающее значения поправочных

коэффициентов.

Следовательно, среднее время наработки до отказа:

Вероятность безотказной работы ячейки за 48 ч:

Таким образом, среднее время наработки функциональной ячейки до отказа

соответствует требованиям технического задания:

T =

46511 часов > TТЗ = 6500 часов.

2.7 Расчет

вибропрочности конструкции ФЯ вычислительного модуля

Целью расчета является оценка вибропрочности конструкции. Конструкция

считается вибропрочной, если в ней отсутствуют механические резонансы, а

допустимая виброперегрузка на резонансной частоте превышает перегрузку,

указанную в техническом задании на изделие.

Отсутствие в конструкции механических резонансов характеризуется следующим

соотношением частоты свободных колебаний f0 любого элемента конструкции и верхней частоты fв диапазона внешних вибрационных воздействий:

Допустимая величина вибрационной перегрузки рассчитывается по формулам:

где: XД - допустимая величина прогиба упругого элемента;

VД - допустимая виброскорость;

μ - коэффициент динамичности конструкции.

Оценка вибропрочности конструкции сводится к расчету частоты свободных

колебаний f0 и допустимой величины виброперегрузки.

где: D - цилиндрическая жесткость

конструкции;

Кэрэ - коэффициент нагрузки со стороны ЭРЭ;

α - коэффициент, зависящий от формы

пластины и условий закрепления на сторонах.

Способ закрепления платы представлен на рисунке 2.3.

где L и B - длина и ширина платы.

Для принятого закрепления платы: p = 1, q =

2,57, r = 5,14.

Цилиндрическая жесткость печатной платы определяется по формуле:

где: h - толщина печатной платы;

E -

модуль упругости материала платы [Н/м2];

ε - коэффициент Пуассона.

E = 33×109 [Н/м2], ε = 0,279, h = 1,76 мм, таким образом:

Для расчета частоты воспользуемся формулой модели тонкой нагруженной

пластины:

где m0

- распределена масса.

где ρ - плотность материала платы [кг/м3], для

стеклотекстолита ρ = 2370.

Коэффициент нагрузки со стороны ЭРЭ:

Кэрэ = 0,7÷0,8.

Таким образом:

Поскольку условие f0 ≥ 2×fв выполняется, т.е. частота свободных колебаний f0 = 170,66 Гц превышает верхнюю границу диапазона

частот внешних вибрационных воздействий fв = 25 Гц, то в разработанной конструкции обеспечивается

отсутствие механических резонансов.

Рассчитаем допустимые величины вибрационных перегрузок на резонансной

частоте конструкции.

Допустимая величина прогиба печатной платы определяется:

где: l - размер меньшей стороны платы, м;

δдоп - допустимая стрела прогиба

материала платы на базовой длине LБ = 1 м. Для стеклотекстолита с

двухсторонним фольгированием δдоп = 11 мм/м2.

Допустимая виброскорость: VД = 800 мм/с = 0,8 м/с, коэффициент

динамичности конструкции μ = 5 для ЭМ1.

Таким образом:

Из двух значений вибрационных перегрузок выбираем минимальное и

сравниваем его со значением, приведенным в ТЗ:

nдоп = min(nx; nv) = min(6,524g;

17,383g) = 6,524g > nТЗ = 2g.

Таким образом, необходимое условие обеспечения вибропрочности выполняется

для разработанной конструкции.

2.8 Оценка

технологичности конструкции ФЯ вычислительного модуля

Анализ технологичности ФЯ вычислительного модуля по конструкторским

показателям.

Радиоэлектронное средство технологично, если при производстве и

эксплуатации (ремонте) его потребительские качества обеспечиваются при

оптимальном (рациональном) расходовании привлекаемых ресурсов [18].

Для количественной оценки технологичности следует рассчитать показатели

технологичности разрабатываемого изделия и сравнить их с нормативными

показателями, представленными в таблице 2.2. Расчеты частных и балльных

показателей также представлены в табл.2.2. Если Бi < 0, то