Разработка управляющей микро-ЭВМ на базе микропроцессора Z80

СОДЕРЖАНИЕ

ВВЕДЕНИЕ

. РАСШИФРОВКА И АНАЛИЗ ТЕХНИЧЕСКОГО ЗАДАНИЯ

. РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ, ИНТЕРФЕЙСА И СТРУКТУРНОЙ

СХЕМЫ

.1 Однокристальная микро-ЭВМ Z80

.1.1 Основные параметры микро-ЭВМ Z80

.1.2 Цоколевка и описание выводов микро-ЭВМ Z80

.1.3 Структура микро-ЭВМ

.2 Разработка структурной схемы

. РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

.1 Модуль ОЗУ

.2 Модуль ПЗУ

. РАЗРАБОТКА СИСТЕМЫ ВВОДА/ВЫВОДА

.1 Модуль генератора тактового импульса

.2 Контроллер клавиатуры и дисплея КР580ВВ79

.3 Интерфейс ввода/вывода

.4 Модуль индикатора

. РАЗРАБОТКА АЛГОРИТМА РАБОТЫ УПРАВЛЯЮЩЕЙ МИКРО-ЭВМ

. РЕАЛИЗАЦИЯ МПС НА БАЗЕ МК

ЗАКЛЮЧЕНИЕ

СПИСОК ЛИТЕРАТУРЫ

ВВЕДЕНИЕ

Микропроцессор

- процессор

<#"697803.files/image001.jpg">

Рисунок

1 - Цоколевка БИСZ80

Назначение

выводов микроконтроллера представлено в таблице 2.

Таблица

2 - Назначение выводов микроконтроллера

|

Вывод

|

Описание

|

Тип

|

|

А0 - А15

|

Шина адреса

|

Выход с 3-мя состояниями

|

|

D0 - D7

|

Шина данных

|

Вход-выход с 3-мя состояниями

|

|

/M1

|

Идентифицирует машинный цикл загрузки кода команды (при

этом активизируется /MREQ

и /RD). При подтверждении прерывания

вместе с ним активизируется /MREQ,

а /RD не активен.

|

Выход

|

|

/MREQ

|

Определяет цикл доступа к памяти, стробируется сигналом /RD или /WR

|

Выход с 3-мя состояниями

|

|

/IORQ

|

Сопровождает операции обращения к портам, стробируется

сигналом /RD или /WR, а адрес порта выдается на А0 - А7. Активизируется

вместе с /M1 при подтверждении прерывания.

|

Выход с 3-мя состояниями

|

|

/RD

|

Чтение данных из памяти или порта

|

Выход с 3-мя состояниями

|

|

/WR

|

Запись данных в память или порт

|

Выход с 3-мя состояниями

|

|

/RFSH

|

Регенерация динамической памяти, при этом активизируется и

/MREQ, а адрес выдается на А0 - А6.

Процесс регенерации Z80

производит перебором 128 адресов, т.е. рассчитан на организацию 16К-словами,

в то время как микросхемы, имеющие объем 64К, требуют регенерации по 256

адресам.

|

Выход с 3-мя состояниями

|

|

/HALT

|

Сигнализирует об остановке процессора

|

Выход

|

|

/WAIT

|

Запрос состояния ожидания.

|

Вход

|

|

/INT

|

Запрос маскируемого прерывания

|

Вход

|

|

/NMI

|

Запрос маскируемого прерывания. Более высокий приоритет,

чем у захвата шины

|

Вход

|

|

/RESET

|

Сброс и инициализация процессора имеет высший приоритет.

Счетчик адреса программ (РС), регистры IX и IY сбрасываются

в нуль. Запросы прерывания INT

запрещаются. Все линии с 3-мя состояниями освобождаются.

|

Вход

|

|

/BUSRQ

|

Запрос на захват управления шинами данных, адреса и

управления.

|

Подтверждение захвата шин (А0 - А15, D0 - D7, /RD,

/WR). После захвата шины процессор не

может выполнять регенерацию динамической памяти.

|

Выход

|

|

Clk

|

Вход приема тактовых сигналов от внешнего ГТИ

|

Вход

|

|

Ucc

|

Питание 5В

|

|

|

GND

|

Общий провод

|

|

2.1.3 Структура микро-ЭВМ

Основу структуры МК (рисунок 2) образует внутренняя 8-битная шина,

которая связывает между собой все устройства БИС:

¾ арифметико-логическое устройство (АЛУ),

¾ устройство управления,

¾ память,

¾ порты ввода-вывода информации.

Структурная схема БИС Z800представлена

на рисунке 2.

Рисунок 2 -Структурная схема БИС Z80

Основное назначение микропроцессора Z80A - обрабатывать данные из памяти

и/или из портов ввода в соответствии с программой. Стартовая программа

расположена в постоянной памяти ROM. Результаты работы по программе Z80A записывает

в оперативную память и/или выводит на устройства вывода. Также возможно, если

это реализовано в программе ROM, загружать различные программы и данные в

оперативную память RAM.

Внутри Z80A имеется программный счетчик PC (Program Counter). Он показывает,

по какому адресу будет считываться очередная команда (операция) из памяти.

После перезагрузки он указывает на ячейку с нулевым адресом (0000H). Содержимое

этого счетчика выдается на шину адреса Z80A при чтении команды.

Также имеется несколько восьмибитных регистров между которыми возможен

обмен данными в процессе выполнения команды. Чаще всего используется регистр A

(Accumulator).Регистр флагов F (flagregisters) используется для ветвления

программы в зависимости от результата операции. Он состоит из нескольких

флагов. Чаще всего используются флаги Z (ZeroFlag) и C (CarryFlag). Проверки

этих двух флагов достаточно для реализации большинства ветвлений по условию в

алгоритмах программ. Флаг Z устанавливается в 1, если в результате операции

число стало равно нулю или при сравнении оказалось, что два числа равны. Флаг С

устанавливается 1, если при вычитании получается отрицательное число или при

сравнении первое число меньше второго.

Постоянная память ROM содержит программу, с которой начинает работу Z80A

после перезагрузки. Программа и данные в этой памяти, в отличии от оперативной

памяти RAM, не стираются при выключении питания. Микропроцессор не может

записывать данные в ROM - только читать. В качестве ROM используем FLASH.

Записывать (прошивать) программы и данные во FLASH будем с помощью

программатора "DIP-32 FLASHER" или другого подходящего для

этой микросхемы программатора.

На плате кроме микросхем разместим также конденсаторы по питанию,

резистор и джампер/перемычку для выбора разных прошивок с помощью старшего

адреса. Но пока перемычку установим и не будем переключать. Краевой разъем на

печатной плате модуля (ZX-BUS CONNECTOR) предназначен для соединения сигналов с

Z80A и ROM с другими модулями микропроцессорной системы.

Шины МК Z80

Микропроцессор Z80 выпускался в 40-выводном DIP-корпусе, наиболее

распространённом для восьмиразрядных микропроцессоров. В отличие от

микропроцессора 8080 фирмы Intel, Z80 для своей работы не требует специфических

дополнительных схем (двухфазного тактового генератора и системного

контроллера), что значительно упрощает конструкцию процессорного модуля. Кроме

того, для работы Z80 требует единственное напряжение питания +5 В вместо трёх

напряжений для 8080 (+5, -5 и +12 В).

Шина адреса

Адреса ячеек ROM, RAM и портов ввода-вывода указываются двумя байтами (16

бит). Для этого у Z80A имеется шина адреса - сигналы A0-A15. 16 битами можно

адресовать 64 Кбайта памяти или портов (адреса от 0 до 65535). При чтении

команды на шину адреса выводится значение программного счетчика PC.

Шина данных

Данные из ROM, RAM и портов ввода считываются байтами (по 8 бит). Также

байтами записываются данные в RAM и порты вывода. Для этого у Z80A имеется шина

данных - сигналы D0-D7.

Шина адреса

Микропроцессор Z80 имеет 16 адресных выходов A15-A0 (номера выводов 5-1,

40-30 соответственно). Активный уровень - высокий; линии имеют три состояния.

Шина данных

У микропроцессора имеется 8 двунаправленных выводов с тремя состояниями

D7-D0 (номера выводов 13, 10, 9, 7, 8, 12, 15 и 14 соответственно). Активный

уровень - высокий.

Шина синхронизации и управления

Шина синхронизации и управления микропроцессора Z80 включает 14 линий.

Регистровая структура микропроцессораZ80

Регистры общего назначения

Микропроцессор Z80 содержит две идентичные группы (банка) из восьми 8-разрядных

регистров в каждой. Эти регистры для краткости именуются регистрами общего

назначения, что, однако, не совсем верно.

Каждый банк состоит из следующих регистров:

аккумулятора A;

регистра флагов F;

регистров общего назначения B, C, D, E, H и L.

Регистры второго банка принято обозначать с помощью знака апострофа: A',

B' и т.д. Функционально регистры обеих групп совершенно идентичны.

Подавляющее число инструкций микропроцессора оперирует с содержимым

регистров первого (основного) банка. Имеются две инструкции (EX AF,AF' и EXX),

которые позволяют обменять местами содержимое банков. Суммарное время

выполнения этих двух команд составляет 8 тактов; время, необходимое для

сохранения тех же самых регистров в стеке с помощью команд PUSH (как это

традиционно делается в обработчиках прерывания для процессора 8080), составляет

44 такта; для восстановления содержимого регистров из стека командами POP

требуется 40 тактов.

Аккумулятор A используется во всех основных арифметико-логических

операций и содержит один из операндов, а также результат операции.

Регистры общего назначения используются вместе с аккумулятором в байтовых

арифметико-логических операциях, храня второй операнд. Кроме того, имеются

инструкции инкремента и декремента содержимого этих регистров. Регистр B,

помимо всего прочего, используется в качестве счётчика в инструкции организации

циклов DJNZ.

Регистры общего назначения могут логически объединяться в три пары BC, DE

и HL, применяющиеся для хранения и обработки 16-разрядных адресов и операндов

(старший байт находится соответственно в регистре B, D и H, а младший - в C, E

и L). Особенно часто это свойство используется для регистровой пары HL,

поскольку система команд включает полный набор арифметико-логических операций

между содержимым аккумулятора и ячейкой памяти, адрес которой находится в этой

регистровой паре (в системе команд микропроцессора 8080 для обозначения такого

операнда использовался “псевдорегистр” M). Правда, арифметико-логические

операции возможны и над операндами, адреса которых хранятся в индексных

регистрах, но коды этих команд занимают 3 байта памяти вместо одного, а для их

выполнения требуется 19 тактов вместо семи.

Адрес в регистровой паре BC может применяться в командах пересылки

8-разрядных операндов, а также в операциях ввода-вывода. Кроме того, содержимое

регистровой пары BC используется в качестве счётчика в инструкциях обработки

блоков данных. Адрес в регистровой паре DE используется в командах пересылки

8-разрядных операндов и обработки блоков данных.

Регистр флагов F состоит из нескольких отдельных разрядов, имеющих

самостоятельное значение. Он имеет следующий формат:

Рисунок 3 - Регистр флагов F

Назначение разрядов регистра флагов следующее(разряд 7) - флаг знака.

Принимает значение 1, если старший (знаковый) разряд результата операции равен

единице.(разряд 6) - флаг нуля. Устанавливается, когда при выполнении операции

был получен нулевой результат.

Разряд 5 не используется.(разряд 4) - флаг вспомогательного переноса.

Устанавливается, когда операция сложения или вычитания вызывает соответственно

перенос из 3-го разряда в 4-й или заём из 4-го разряда в 3-й. Используется при

выполнении операций десятичной коррекции инструкцией DAA.

Разряд 3 не используется./V (разряд 2) - этот флаг в зависимости от

операции является либо признаком переполнения (V), либо признаком чётного

результата (P). В первом случае он устанавливается, если при выполнении

операции произошло переполнение, и сбрасывается при отсутствии такового. Во

втором случае он устанавливается, если в результате присутствует чётное число

единичных разрядов, и сбрасывается, если единиц нечётное число.(разряд 1) -

флаг операции вычитания. Устанавливается, если предыдущая операция была

операцией вычитания, и сбрасывается в противном случае. Используется

инструкцией DAA при выполнении десятичной коррекции результата.(разряд 0)

устанавливается, если при выполнении операции сложения произошёл перенос из

старшего разряда или если при выполнении операции вычитания произошёл заём в

старший разряд. В инструкциях сдвига во флажок переноса заносится значение

выдвигаемого разряда.

При выполнении некоторых инструкций те или иные флаги регистра F

устанавливаются или сбрасываются по особым правилам. Сведения об имеющихся

особенностях приводятся в описании системы команд.

Индексные регистры

Два 16-разрядных индексных регистра IX и IY используются в некоторых

инструкциях для адресации операндов в памяти. Адрес ячейки памяти вычисляется

путём сложения содержимого индексного регистра с 8-разрядной константой d,

являющейся частью кода команды. Первоначальное содержимое индексного регистра

при этом не изменяется.

Счётчик команд

-разрядный счётчик команд PC содержит адрес следующей команды, подлежащей

выполнению. Когда очередная команда выбрана из памяти, его значение

увеличивается на длину кода команды. При выполнении инструкций переходов

содержимое счётчика команд замещается на адрес перехода; при выполнении команды

вызова подпрограммы или при прерывании текущее содержимое PC сохраняется в

стеке.

Прочие регистры

-разрядный регистр адреса регенерации R хранит адрес очередной строки

динамической памяти, которая подлежит регенерации. Очередной цикл регенерации

выполняется сразу после выборки первого (или единственного) байта кода

операции, благодаря чему регенерация динамического ОЗУ совмещена по времени с

обработкой информации в процессоре и не приводит к лишним потерям времени на

ожидание её завершения. После выполнения очередного цикла содержимое младших

семи разрядов регистра R автоматически увеличивается на единицу. Значение

старшего разряда не изменяется.

Ценность встроенного счётчика регенерации снижается из-за того, что он

формирует 7-, а не 8-разрядный адрес строки ОЗУ, подлежащей регенерации. Когда

микропроцессор Z80 создавался, этот недостаток не играл существенной роли,

поскольку самыми распространёнными микросхемами динамической памяти были

кристаллы ёмкостью 128×128 разрядов (16 Кбит), для регенерации

которых требовались 7-разрядные адреса. Позднее появились кристаллы с

организацией 256×256 разрядов (64 Кбит); для их

регенерации требовались уже 8-разрядные адреса

-разрядный регистр адреса таблицы прерываний I используется в “родном”

(втором) режиме обработки прерываний микропроцессора Z80. В нём содержится

старший байт адреса таблицы, в которой хранятся указатели обработчиков

прерываний. Младший байт, называемый вектором прерывания и определяющий, в

каком из элементов этой таблицы хранится указатель нужного обработчика,

выдаётся устройством, запросившим прерывание.

В нулевом и первом режимах обработки прерываний регистр I не

используется.

Система прерываний

Микропроцессор Z80 обслуживает два класса прерываний: немаскируемые и

маскируемые (8080 имел единственный класс прерываний - маскируемые).

Система команд

Система команд микропроцессора Z80 насчитывает 158 инструкций, из которых

78 полностью повторяют (правда, зачастую с иной мнемоникой и другим способом

записи операндов) команды процессора 8080, благодаря чему часто достигается

полная переносимость программного обеспечения.

2.2 Разработка структурной схемы

¾ однокристальная микро-ЭВМ Z80 - микросхема, предназначенная для управления электронными

устройствами;

¾ память, состоящая из ПЗУ и ОЗУ, в качестве которых по

техническому заданию используются такие БИС памяти, как КР537РУ10 и К541РТ2

соответственно (ПЗУ - энергонезависимая память, используется для хранения

массива неизменяемых данных.ОЗУ - техническое устройство, реализующее функции

оперативной памяти.);

¾ параллельный интерфейс для подключения интерфейсных

устройств;

¾ Интерфейс ввода/вывода;

¾ Генератор тактовых импульсов (ТИ);

Структурная схема микро-ЭВМ представлена на рисунке 4

Рисунок 4 - Структурная схема микро ЭВМ

К системной шине подключаем микроконтроллер, основную память, состоящую

из ОЗУ и ПЗУ, клавиатуру и генератор ТИ для ввода/вывода информации

соответственно. Через параллельный интерфейс к шине подключаем аналого-цифровой

преобразователь, на который поступают сигналы с датчика

3. РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

.1 Модуль ОЗУ

Для расширения памяти данных микроконтроллера в соответствии с заданием

выберем КР537РУ10.

Микросхема ОЗУ серий К537 относятся к типу асинхронного статического ОЗУ,

поэтому достаточно просты в применении.

Технические характеристики ОЗУ КР537РУ10 представлены в таблице 3.

Таблица 3 - Характеристики БИС КР537РУ10

|

Тип микросхемы

|

Емкость, бит

|

tц.зп (сч)

|

Uпит, В

|

Рпот, Вт

|

Тип корпуса

|

|

|

|

|

0,42

|

|

|

КР537РУ10

|

2К×8

|

1000

|

5+ 10%

|

|

239.24-2

|

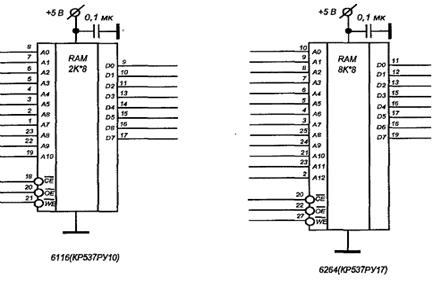

Цоколевка микросхемы представлено на рисунке 5.

Рисунок

5 - Цоколевка ОЗУКР537РУ10и КР537РУ17

Обозначение

выводов ОЗУ представлено в таблице 4.

Таблица

4. - Назначение выводов

|

Вывод

|

Назначение

|

Вывод

|

Назначение

|

|

№1

|

Вход адресный строки А3

|

№13

|

Вход-выход данных DI/04

|

|

№2

|

Вход адресный строки А4

|

№14

|

Вход-выход данных DI/05

|

|

№3

|

Вход адресный строки А5

|

№15

|

Вход-выход данных DI/06

|

|

№4

|

Вход адресный строки А6

|

№16

|

Вход-выход данных DI/07

|

|

№5

|

Вход адресный столбца А7

|

№17

|

Вход-выход данных DI/08

|

|

№6

|

Вход адресный столбца А8

|

№18

|

Вход сигнала «Выбор микросхемы» CS

|

|

№7

|

Вход адресный столбца А9

|

№19

|

Вход адресной строки А0

|

|

№8

|

Вход адресный столбца А10 данных ОЕ

|

№20

|

Вход сигнала разрешения выдачи

|

|

№9

|

Вход-выход данных DI/01 WR/RD

|

Вход сигнала «Запись-считывание»

|

|

№10

|

Вход-выход данных DI/02

|

№22

|

Вход адресной строки А1

|

|

№11

|

Вход-выход данных DI/03

|

№23

|

Вход адресной строки А2

|

|

№12

|

Общий вывод 0V

|

№24

|

Вывод питания от источника напряжения U

|

Внешняя память данных представляет собой одну или несколько

самостоятельных микросхем памяти. Чаще всего используют статическую память с

байтовой организацией объемом 2К*8 или 8К*8 бит (1К = 1024). Такие микросхемы;

имеют 8 выводов данных (D0-D7), по которым осуществляется одновременная запись

в микросхему всех 8 бит в выбранную ячейку памяти или чтение 8 бит из этой

ячейки.

Структурная схема БИС КР537РУ10 показана на рисунке 6.

Рисунок 6 - Структурная схема БИС КР537РУ10.

3.2 Модуль ПЗУ

Микросхемы программируемых ПЗУ по принципу построения и функционирования

аналогичны масочным ПЗУ, но имеют существенное отличие в том, что допускают

программирование на месте своего применения пользователем. Операция

программирования заключается в разрушении (пережигании) части плавких перемычек

на поверхности кристалла импульсами тока амплитудой 30... 50 мА. Технические

средства для выполнения этой операции достаточно просты и могут быть построены

самим пользователем. Это обстоятельство в сочетании с низкой стоимостью и

доступностью микросхем ПЗУ обусловило их широкое распространение в

радиолюбительской практике.

В данном курсовом проекте рассматривается применение

микросхемы ПЗУ К541РТ2. Микросхемы ПЗУ серии К541 выполнены по технологии ИИЛ.

Основные характеристики микросхемы представлены в

таблице 5.

Таблица 5 - Характеристики БИС К541РТ2

|

Тип микросхемы

|

Емкость, бит

|

Рпот, мВт

|

Тип выхода

|

|

|

770

|

|

|

К541РТ2

|

2К×8

|

|

ТТЛ-ОК

|

Матрица до программирования, т. е. в исходном

состоянии, содержит однородный массив проводящих перемычек, соединяющих строки

и столбцы во всех точках их пересечений. Перемычки устанавливают из

поликристаллического кремния. Перемычка в матрице выполняет роль ЭП. Наличие

перемычки кодируют логической 1, если усилитель считывания является

повторителем, и логическим 0, если усилитель считывания - инвертор.

Следовательно, микросхема ПЗУ в исходном состоянии перед программированием в

зависимости от характеристики выходного усилителя может иметь заполнение

матрицы либо логическим 0, либо логической 1.

Цоколевка данной ПЗУ представлена на рисунке 7

Рисунок 7 - Микросхема ПЗУ К541РТ2

Назначение выводов ПЗУ К541РТ2 представлено в таблице

6.

Таблица 6 - Описание выводов БИС ПЗУ К541РТ2

|

Обозначение вывода

|

Номер контакта

|

Назначение вывода,

|

Состояние

|

|

D (0-7); (-)

|

17; 16; 15; 14; 13; 11; 10; 9;

|

Выход данных

|

0,1

|

|

А (0-10); (а)

|

8; 7; 6; 5; 4; 3; 2; 1; 23; 22; 19

|

Входы данных с локальной шины МП

|

0,1

|

|

CS (1-3); (ВМ)

|

18

|

Выбор микросхемы; L-уровень сигнала подключает ПЗУ к

системной шине

|

0,1

|

|

UCC; (UНП)

|

26

|

Напряжение питания (+5 В)

|

1

|

|

GND (Общ)

|

7

|

Общий вывод микросхемы

|

0

|

Структурная схема микропроцессора представлена на рисунке 8.

Рисунок 8 - Структурная схема БИС К541РТ2.

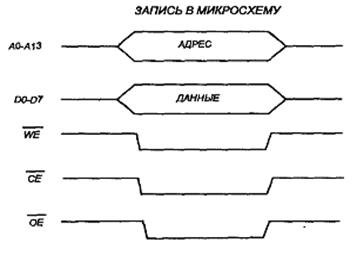

Работа с подобными микросхемами должна осуществляться следующим образом.

Положим, мы хотим записать число 145D = 10010001В в ячейку с адресом 84D = 54Н

= 1010100В. Для этого МК должен установить записываемое число на линиях данных

D0-D7 микросхемы (D0=D4=D7=1, D1=D2-D3=D5=D6=0), а адрес ячейки - на адресных

линиях (А2=А4=А6=1, А0=А1=АЗ=А5=0; А7, А8 и последующие старшие адреса вплоть

до А10 для микросхем объемом 2К* 8 или до А12 для микросхем 8К*8 также должны

быть установлены в 0). Установив адресную информацию и данные, МК одновременно

с этим или чуть позже должен установить 0 на входе WE микросхемы (будет запись)

и 0 на СЕ (знак того, что мы обращаемся именно к этой микросхеме). Как только

после этого на входе ОЕ микросхемы памяти МК установит 0, осуществится запись

числа 145 в ее 84-ю ячейку.

Соответственно, если мы хотим прочитать данные из все той же, к примеру,

84-й ячейки, мы должны, как и в предыдущем случае, установить адрес ячейки на

адресных линиях, и одновременно с этим или чуть позже установить 1 на входе WE

микросхемы (будет чтение) и 0 на СЕ (знак того, что мы обращаемся именно к этой

микросхеме). Как только после этого на входе ОЕ микросхемы памяти МК установит

0, осуществится чтение числа из выбранной ячейки, и оно появится на линиях

данных D0-D7 микросхемы памяти. Сказанное поясняется временными диаграммами,

приведенными на рисунке 9.

Рисунок 9 - Диаграммы чтения и записи микросхем памяти

4.

РАЗРАБОТКА СИСТЕМЫ ВВОДА/ВЫВОДА

.1 Модуль

генератора тактового импульса

Генератор тактовой частоты (генератор тактовых

импульсов) генерирует электрические импульсы заданной частоты (обычно

прямоугольной формы) для синхронизации различных процессов в цифровых

устройствах - ЭВМ, электронных часах и таймерах, микропроцессорной и другой

цифровой технике. Тактовые импульсы часто используются как эталонная частота -

считая их количество, можно, например, измерять временные интервалы.

Рисунок 10 - БИС тактового генератора КР580ГФ24

Назначение выводов генератора тактовых импульсов

показано в таблице 7.

Таблица 7 - Назначение выводов тактового генератора

КР580ГФ24

4.2 Контроллер клавиатуры и дисплея КР580ВВ79

Программируемое интерфейсное устройство, предназначенное для ввода и

вывода информации в системах, выполненных на основе 8- и 16-разрядного

микропроцессора КР580ВМ80. Кроме того, микросхема может применяться и как

самостоятельное устройство при выполнении требований, предъявляемых к

электрическим и временным параметрам.

Клавиатурная часть обеспечивает ввод информации в микросхему через линии

возврата RET7-RET0 с клавиатуры (клавиатурная матрица объемом 8 слов*8 разрядов

с возможностью расширения до 4*8 слов*8 разрядов) и матрицы датчиков (8 слов*8

разрядов), а также ввод по стробирующему сигналу (8 слов*8 разрядов). Для

хранения информации в микросхеме предусмотрено 8 байт ОЗУ.

Дисплейная часть микросхемы обеспечивает вывод информации по 4-разрядным

каналам DSPA3-DSPA0 и DSPB3-DSPB0 в виде двоичного кода на 8- и 16-разрядные

цифровые или алфавитно-цифровые дисплеи.

Цоколевка микросхемы представлено на рисунке 11.

Рисунок 11 - Цоколевкамикросхемы КР580ВВ79

Таблица 8 - Назначение выводов микросхемы КР580ВВ79

|

Вывод

|

Обозначение

|

Назначение выводов

|

|

1, 2, 5-8, 38, 39

|

RET2-RET7, RET0, RET1

|

Линии возврата

|

|

3

|

C

|

Синхронизация

|

|

4

|

INT

|

Запрос прерывания

|

|

9

|

SR

|

Установка

|

|

10

|

RD

|

Чтение информации

|

|

11

|

WR

|

Запись информации

|

|

1-19

|

D0-D7

|

Канал данных

|

|

20

|

GND

|

Общий

|

|

21

|

INS/D

|

Команда / данные

|

|

22

|

CS

|

Выбор микросхемы

|

|

23

|

BD

|

Гашение отображения

|

|

24-27

|

DSPA3-DSPA0

|

Канал дисплея А

|

|

28-31

|

DSPB3-DSPB0

|

Канал дисплея В

|

|

32-35

|

S0-S3

|

Линии сканирования

|

|

36

|

SH

|

Сдвиг

|

|

37

|

CO/STB

|

Управление стробирующий сигнал

|

|

40

|

Ucc

|

Напряжение сигнала

|

.3 Интерфейс ввода/вывода

Микросхема INF8574AN предназначена для организации интерфейса между

8-разрядной параллельной шиной данных и I2C-шиной. Конструктивно

микросхема выполнена в 16-выводном DIP-корпусе.

Особенности БИС:

• Ток потребления в статическом режиме до 10 мкА

• Максимальная тактовая частота 100 кГц

• Выход прерывания с открытым стоком

• Три адресных входа для возможности наращивания в

системе до 8 аналогичных микросхем

• Выходы порта ввода/вывода с высоким выходным током

для возможности прямого управления светодиодами

• 8-разрядный двунаправленный порт ввода/вывода

• Двухпроводной последовательный I2C

интерфейс

Микросхема содержит 8-разрядный двунаправленный порт

ввода/вывода, схему управления I2C-шиной, сдвиговый регистр, схему

формирования сброса по включению питания, логику прерываний.

Структурная схема интерфейса показано на рисунке 12.

Рисунок 12 - Структурная схема блока интерфейса

ввода/вывода

Выполняемые функции:

• Прием по I2C-шине последовательных

данных, преобразование их в параллельные и выдача через8-разрядный порт

ввода/вывода;

• Прием через порт ввода/вывода параллельных данных,

преобразование их в последовательные и передача по I 2 C-шине;

• Формирование сигнала запроса прерывания при

изменении данных на входах порта ввода/вывода в режиме чтения.

4.4

Модуль индикатора

Для непосредственного отображения информации в устройствах динамической

цифровой индикации используются семисегментные индикаторы, ЖК-матрицы и др.

Заданное устройство требует использования семисегментных индикаторов с общими

катодами, выбор которых целесообразно осуществить из диапазона индикаторов с

малым прямым током (5 - 10 мА). Всего потребуется n=5 индикаторов, подключенных

анодами к преобразователю кода и катодами к дешифратору.

Структурная схема индикатора показана на рисунке 13.

Рисунок 13 - Структурная схема блока индикатора

Для построения устройства динамической цифровой индикации выберем ССИ

АЛ304А, который отличается низким рабочим напряжением и током.

Принципиальная схема данного индикатора изображена на рисунке 14.

Рисунок

14- Принципиальная схема АЛ304А

Таблица

9 - Основные параметры светоиндикатора АЛ304А

|

Светоиндикатор

|

Мккд (м2)

|

при

|

Iпр. max, мА

|

Обозначение цвета свечения

|

Схема включения

|

|

|

Uпр, В

|

Iпр, мА

|

|

|

|

|

АЛ304А

|

140

|

2

|

5

|

11

|

К

|

ОК

|

5. РАЗРАБОТКА АЛГОРИТМА РАБОТЫ УПРАВЛЯЮЩЕЙ МИКРО-ЭВМ

микропроцессор память генератор контроллер

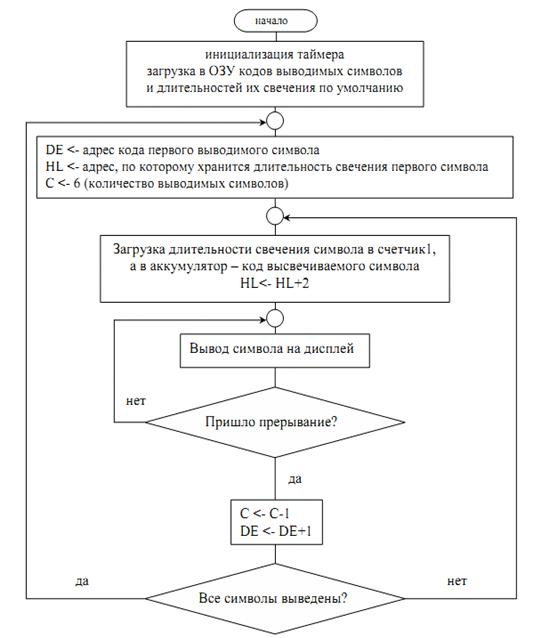

Алгоритм работы управляющей программы представлен на рисунке 15.

Рисунок

15 - Алгоритм работы программы

6. РЕАЛИЗАЦИЯ МПС НА БАЗЕ МК

Тема электронных квартирных звонков неоднократно обсуждалась на страницах

различных радиолюбительских журналов, и, тем не менее, всегда вызывает живой

интерес, т. к. с одной стороны, звонок, имеющий даже самый красивый и приятный

звук, рано или поздно надоедает, а с другой, всегда можно придумать что-то

оригинальное, свое, ни на что не похожее. Предлагаю на суд читателей

электронный звонок, собранный на основе популярного 8-разрядного

микропроцессора Z-80, который умеет "проиграть'' в динамик любой

оцифрованный звук с частотой дискретизации 22 кГц и длительностью больше

секунды.

Данная оцифровка записана в УФ-ПЗУ совместно с маленькой исполняемой

программкой в машинных кодах Z-80. Применение перепрограммируемой ПЗУ

обуславливает легкость смены звука звонка без применения паяльника. Кстати,

выбор в качестве основы процессора Z-80 продиктован в основном дешевизной и

общедоступностью оного. И хоть конструирование звонка на базе целого

микроконтроллера сильно напоминает "забивание гвоздей наручными

часами", тем не менее, в результате получилось, на мой взгляд, дешево и

сердито.

Схема представлена на рисунке 16.

Рисунок 16- Схема музыкального звонка

В качестве памяти использована микросхема 27C512, занимающая все адресное

пространство процессора, а в качестве порта - регистр 1533ИР23. Выходы регистре

Q0 - Q7 соединены с простейшим резисторным цифроаналоговым преобразователем,

формирующим уже готовый звуковой сигнал, который осталось отфильтровать от

нежелательных ультразвуковых составляющих конденсатором С1, отрегулировать по

наиболее подходящей громкости потенциометром R17 и усилить по мощности

микросхемой К174УН14. Мощности усилителя вполне достаточно даже пользователям с

пониженным слухом.

Поскольку процессор работает только с одним кристаллом памяти, только в

режиме чтения и только с одним портом в режиме записи, оказалось возможным

полностью отказаться от дешифратора адреса и максимально упростить схему выбора

кристаллов, задействовав только два сигнала MREQ и IORQ процессора. Сброс

организован на элементах R21, С7 и VD1, задающий генератор, вырабатывающий

меандре частотой 4МГц, выполнен на элементах DD3.1 и DD3.2. с применением

кварцевого резонаторе BQ1. Запускается звонок по приходу лог. "0" на

вход аппаратного маскируемого прерывания (сигнал INT). Узeл DD3.5, DD3.6, R23,

С8, VD3 служит для защиты от помех, возникающих на проводах, ведущих к

звонковой кнопке КН. Цифровая часть звонка питается напряжением +5В,

стабилизированным микросхемой КР142ЕН5А.

А дальше, с адреса 00A0H и до конца (FFFFH) находится оцифрованный

звуковой сигнал который можно получить из обыкновенного звукового файла .WAV MS

WINDOWS формата 22 кГц МОНО. Единственное, что нужно сделать перед тем, как

использовать такой файл - удалить его заголовок в любом простом редакторе

(например, встроенным в Volkov Commander).

ЗАКЛЮЧЕНИЕ

В настоящей работе предложена схема электрическая принципиальная микропроцессорной

системы для отображения буквенно-цифровой информации на матричном светодиодном

дисплее размерностью 16x8.

Приведен программный код МС на языке Ассемблер, реализующий базовую

функциональность в соответствии с рабочим заданием.

Предложенная система является универсальной и может быть использована,

например, для отображения времени. Круг задач решаемых системой может быть

расширен, при дополнении ее дополнительными портами ввода-вывода дискретных

сигналов, что позволит считывать информацию с внешних датчиков и управлять,

внешними схемами, например, электромагнитными реле и двигателями.

К ограничениям разработанной системы можно отнести частичную дешифрацию

адресного пространства памяти, не позволяющую нарастить объем системной памяти

(ПЗУ, ОЗУ) добавлением дополнительных ИС запоминающих устройств. Схемотехника

устройства могла бы быть упрощена при использовании вместо однокристального

микропроцессора Z80, микроконтроллера со встроенной памятью. Для этих целей

могли бы быть использованы, например, отечественные K1816ВЕ51 или современные

микроконтроллеры фирм Atmel, Microchip. Разработанная схема в полном объеме

удовлетворяет рабочему заданию на курсовое проектирование в связи с чем

процедуру ее проектирования можно считать завершенной.

Сколько бы не совершенствовалась эта курсовая, в ней не может быть

рассказано всё о микропроцессоре Z80. «Учтите, что любая программа практически

никогда не может быть завершена, поэтому программист должен сам решить, когда

наступает пора ему остановиться», - поучает нас П. Нортон в одной из своих

книг. Подобные рассуждения применимы и к завершённости курсовой.

Если ваш компьютер делает всё, что вам нужно, если вы не профессиональный

программист или разработчик микросхем, знания о работе микропроцессора на этом

уровне могут послужить лишь удовлетворению вашего интеллектуального

любопытства, не более того. Сложно сказать об описании микропроцессора на столь

детальном уровне что-либо более ёмкое.

Остаётся надеяться, что данная курсовая будет служить не только для

удовлетворения любопытства, а также и как некий справочник по микропроцессору

Z80.

СПИСОК ЛИТЕРАТУРЫ

1. Мочалов

М.Ю. Основы микропроцессорной техники. Чебоксары: Изд-во Чуваш. ун-та, 2004.

103 с.

. Щелкунов

Н.Н., Дианов А.П. Микропроцессорные средства и системы. М.: Радио и связь,

1989. 267 с.

. Микросхемы

ТТЛ. Том 1. Пер. с нем. М.: ДМК Пресс, 2001. - 384 С.

. Лебедев

О.Н. Микросхемы памяти и их применение. М.: Радио и связь, 1990. 158 с.

. Применение

интегральных микросхем памяти: Справочник /А.А. Дерюгин, В.В. Цыркин, В.Е.

Красовский и др.; Под ред. А.Ю. Гордонова. А.А. Дерюгина. - М.: Радио и связь,

1994. -232с.

. МАШИННЫЕ

КОДЫ издательство “СОЛОН” 1993 г.

. В.Ф.

Королев "Микропроцессор Z80"