Сравнительный анализ критериев эффективности инвестиционных проектов

1. Алгоритм работы

блока сложения дробных двоичных чисел в обратном модифицированном коде с фиксированной

запятой

Целью данного

проектирования является блок сложения двоичных чисел с фиксированной запятой,

операнды поступают в блок в прямом коде, в блоке используется обратно

модифицированный код. Формат операндов n=10. Блок вырабатывает флаги S,P,Z,OVR. Серия 155.

Рис 1 Общая структура БCДЧфз

1.1 Описание формата

данных и результата, применяемых в операции проектируемого блока

Рис 2, Формат чисел А, В,

С в прямом коде, десятиразрядный

D0-D8 – разряды числа

D9 – знаковый разряд

Диапазон:

Min = - 1111111112 = -511

Max = + 1111111112 = 511

Рис 3, Формат чисел А, В,

С в обр.мод. коде, одиннадцатиразрядный

D0-D8 – разряды числа

D9,D10 – знаковый разряд

Флаги используемые в

блоке:

S – флаг знака разряда результата

определяется разрядом D9(D10).

S = 0 если в знаковом разряде D9 "0".

S = 1 если в знаковом разряде D9 "1".

Р – флаг паритета (или

чётность результата).

Р = 1 если количество "1"

числе чётно.

Р = 0 если кол-во "1"

в числе не чётно.

Z – флаг нулевого результата.

Z = 1 если все разряды за исключением знакового

должны быть равны 0. Z = 0

если есть наличие 1 в одном из разрядов числа, за исключением знакового.

OVR – флаг переполнения. OVR = 1 в случае когда произошло

переполнение (ЗН1≠ЗН2). OVR =

0 переполнения нет (ЗН1=ЗН2).

1.2 Словесное описание работы блока Сложения

С шины данных в прямом

коде подаются числа А и В формата n=10. Операнд А из прямого кода переводится в обратно модифицированный код,

операнд В также переводится из прямого кода в обратно модифицированный. После

перевода операнды складываются. После этого начинаются вырабатываться флаги: Z, P, S, OVR .

Операнд С переводится из

обратно модифицированного в прямой код и выдается на шину данных.

2. Выбор и обоснование схемы электрической

структурной БСДЧфз

Основой для построения

схемы электрической является блок-схема алгоритма, в которой каждая микро

операция заменяется блоком комбинационной схемы или устройством, представленным

в виде прямоугольников, в которых указываются разрядность входа и выхода.

Помимо этого в структурной схеме должны быть указаны у тех устройств которые

имеют шины приема, сдвига и выдачи числа (регистры, счетчика и др.,) сигналы

синхронизации, которые определяют последовательность выполнения микроопераций

во времени.

2.1 Описание состава

основных узлов и управляющих сигналов проектируемого блока по схеме

электрической структурной

Рг.1 и Рг.2 являются

параллельными 10-разрядным регистрами, предназначенными для приема и хранения

операндов А и В в прямом коде с фиксированной запятой. Сигналы CS1 и CS2 служат для приема операндов А и В прямом коде на RG1 и RG2. Преобразователь кода Пр.К.1 и Пр.К.2 служат для перевода

чисел [A] и [B] из прямого кода в обратно модифицированный. См.1 производит

сложения десяти разрядных операндов [A] и [B] в обратно модифицированном коде.

Блок 2 служит для

определения флага OVR

(переполнения). Преобразователь кода 3 служит для перевода результата [C] из обратно модифицированного в

прямой код.

Блок 4 служит для

определения флагов S,P,Z.

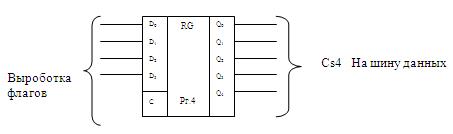

Регистры Рг.3 служат для

хранения и получения десяти разрядного результата [C] и Рг.4 (четырёх разрядный) служит для хранения флагов S,P,Z,OVR (Рг.4).

2.2 Описание принципа работы блока сложения

по схеме электрической структурной

В соответствии со схемой

электрической структурной (рис. 4) С шины данных поступают числа [А] и [B] в прямом коде, которые записываются

по сигналам CS1 и CS2 в регистрах Рг.1 и Рг.2.

После этого число [А] и [B] преобразуются из прямого кода в

обратно модифицированный код при помощи логических элементов "исключающих

или".

Затем оба числа попадают в сумматор

СМ1, где они сложатся и появится результат [С].

Будет произведена проверка на наличие

переполнения блоком 2, в случае переполнения на регистр Рг3 поступит уровень

логической "1", в противном случае "0".

После чего результат поступит на

преобразователь кода и будет преобразована в прямой код.

Произойдёт проверка флагов S, P, и Z,

результаты поступят на регистр Рг3.

Затем после выполнения всех операций

число будет записано в Рг4 по сигналу CS3 и отправлено на шину данных.

А в Рг5 будут записаны все флаги по

сигналу CS4 и затем отправлены на шину данных.

3. Выбор и обоснование

схемы электрической функциональной блока сложения двоичных чисел в обратном

модифицированном коде

Данная электрическая

функциональная схема блока сложения двоичных чисел в обратном модифицированном

коде, строится на основе схемы электрической структурной блока сложения

двоичных чисел в обратном модифицированном коде.

3.1 Выбор функциональных узлов блока

сложения двоичных чисел в обратном модифицированном коде

1. Рг. 1 – параллельный десятиразрядный регистр. Служит

для приема числа [А] с шины данных в прямом коде.

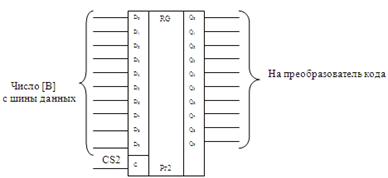

2. Рг 2 – параллельный десятиразрядный регистр. Служит

для приема числа [В] с шины данных в прямом коде.

3. Рг. 3 – параллельный десятиразрядный регистр. Служит

для приема результата [С].

4. Рг 4 – параллельный четырёх разрядный регистр. Служит

для приема флагов с блока выработки флагов.

5.См.1- Сумматор.

Предназначен для сложения чисел [А] и [В] в обратно модифицированном коде.

3.2 Синтез и анализ

комбинационных схем

Блок 2. Определение

переполнения. Данный блок построен на элементе "Исключающее или" .

Блок 4. Определение

флагов S,P,Z,OVR.

S – служит для определения знака числа,

берётся из старшего разряда в знаковой области результата.

Р – Флаг паритета

Z – Служит для определения равенство

числа к 0. Строится на элементе "9Или-не"

Преобразователь кода.

Преобразователь кодов из

прямого в обратно модифицированный и наоборот (Пр.К.1,Пр.К.2,Пр.К.3) Блок

преобразования кода строится на элементе "Исключающий или".

Трёхразрядный

ПрК из прямого кода в дополнительный модифицированный.

По аналогии с

данным ПрК строятся преобразователи кода на любое количество разрядов.

3.3 Временные диаграммы

работы проектируемого блока

Tвып.опер.= t1+t2+t3+t4

CS1 – приём числа [A]пр. на

Рг.1 с шины данных.

CS2 – приём числа [B]пр. на

Рг.2 с шины данных.

CS3 – приём результата [C]пр. с

преобразователя кода.

CS4 – приём флагов S, P, Z, OVR на Рг.4.

t1= Рг.1

t2= Рг.2

+Пр.К+См.1+Пр.К

t3= Рг.3

+Бл2+Бл.3

t4= Рг.4

3.4 Описание принципа работы блока сложения по схеме

электрической функциональной

C 10-и разрядной шины данных на входы регистров Рг.1 и Рг.2 с

управляющими сигналами Cs1 и CS2 поступают числа [A] и [B] в прямом коде. Затем числа A и B поступают на

преобразователи кодов, реализованных на элементах "исключающее или" и

преобразуется из прямого в обратно модифицированный код . Затем числа A и B в обратно модифицированном коде поступают на сумматор Сум.1.

Полученный результат [C] поступает

в преобразователь кода, где преобразуется из обратно модифицированного в прямой

код (при переполнении разрядной сетки знакового числа [C], знак результата в прямом коде будет взят из младшего

разряда знаковой части результата [C] в обратно модифицированном коде). Происходит заполнение флагов: S, P, Z, OVR . Результат в прямом коде поступает

с управляющим сигналом Cs3 и

записывается в регистр Рг.3. В регистре Рг.4 записываются все флаги с

управляющем сигналом CS4.

4. Выбор и обоснование

схемы электрической принципиальной проектируемого блока

Схема электрическая

принципиальная БСДЧФЗ строится на основании разработанной функциональной схемы

и сери интегральных микросхем 155.

Схема электрическая

принципиальная БСДЧФЗ представлена на листе МТКП.4302175.000

4.1 Серия 155 (SN74)

Тип схемотехнической

реализации выполняемых функций: ТТЛ.

Типовые параметры:

Время задержки

распространения 10нс;

Удельная потребляемая

мощность 10мВт/ЛЭ;

Работа переключения

10пДж;

Коэфицент разветвления по

выходу 10;

Напряжение питания +5В;

Выпускается в

пластмассовых (155, к155), металлокерамических (км155) и стеклокерамических

(с155) корпусах с вертикальным расположением выводов типа DIP.

Отклонение

напряжения питания от номинального значения ±5%

Диапазон рабочих температур

Для 155, к155 -10 +70оС

Для км155, с155 -45 +85оС

Предельно допустимые

значения параметров и режимов эксплуатации ИС к155, км155 в диапазоне рабочих

температур кратковременное, в течение 5мс, напряжение питания 7В, максимальное

постоянное напряжение питания 5,25В.

4.2 Особенности

реализации функциональных узлов и элементов БУДЧФЗ на выбранных элементах и узлах

серии 155

Для реализации десяти

разрядных регистров Рг.1, Рг.2, Рг.3 используются два регистра: -

восьмиразрядный универсальный регистр сдвига 155ИР13, на информационные входы

подаётся код числа, S0=S1=1, на вход С подаётся тактовый импульс, DR и DL произвольно, R=1.

Для реализации преобразователя

кода из прямого в обратный код и на оборот используется 9 элементов "исключающий

или" ЛП5.

Для реализации одиннадцати

разрядного сумматора в схеме используются три четырёх разрядных АЛУ 155ИП3,

выход С4 первого соединяется со входом С0 следующего, М- вход выбора режима, Е-

вход кода операции.

Для реализации "блока

2" (определение переполнения), используется элемент "исключающий или"

155 ЛП5 (см.выше).

|

Обозначение узла элемента на

схеме Э2

|

Название и тип узла элемента в

схемах Э2, Э3

|

Обозначение узла элемента Э3

|

Тип узла элемента в серии

|

Количество корпусов микросхем шт

|

Количество элементов в корпусе

|

|

1

|

2

|

3

|

4

|

5

|

6

|

|

DD1, DD2

|

Регистр 10 разрядный

|

DD1,DD2

DD3,DD4

|

К155ИР13

|

4

|

1

|

|

DD3,DD4

|

Преобразователь кода "искл. или"

|

DD5-DD7

DD8-DD10

|

155ЛП5

|

6

|

4

|

|

DD5

|

АЛУ выполняет функцию сумматора

|

DD11-DD13

|

K155ИП3

|

1

|

|

DD6

|

Флаг переполнения

"искл. или"

|

DD18

|

155ЛП5

|

1

|

4

|

|

DD7

|

Преобразователь результата

|

DD15-DD17

|

155ЛП5

|

3

|

4

|

|

DD8

|

Флаг равнозначности 0

|

DD23

DD24

DD14

|

К155ЛЕ4

К155ЛА4

155Лн1

|

1

1

1

|

3

3

6

|

|

DD9

|

Регистр 10 разрядный

|

DD19,DD20

|

К155ИР13

|

2

|

1

|

|

DD10

|

Флаг чётности

|

DD21,DD22

DD14

|

155ЛП5

155Лн1

|

2

1

|

4

6

|

|

DD11

|

Регистр флагов 4 разрядный

|

DD25

|

К155ИР13

|

1

|

1

|

|

Тип микросхемы

|

Ток потребления

|

Задержка в мС

|

tср

НС

|

|

t01

|

t10

|

|

1

|

2

|

3

|

4

|

5

|

|

К155ИР13

|

116

|

26

|

35

|

30,5

|

|

155ЛП5

|

50

|

22

|

27,5

|

|

К155ИП3

|

150

|

50

|

50

|

50

|

|

К155ЛЕ4

|

6,8

|

15

|

15

|

15

|

|

К155ЛА4

|

16,5

|

15

|

22

|

18,5

|

|

155ЛН1

|

33

|

22

|

15

|

18,5

|

4.3 Описание работы

проектируемого блока по схеме электрическая принципиальная

На входы регистров Рг.1

микросхем DD1 и DD2 поступает число [А] с 10-и разрядной шины данных в прямом

коде на входы D0-D7 микросхемы DD1 и

входы D0-D1 микросхемы DD2, с

управляющим сигналом CS1.

Аналогично поступает

число [B] на микросхемы DD3,DD4.

После, число [А] и [В] в

прямом коде поступают на преобразователи кодов построенных на элементах " искл.

или " и реализованных на микросхемах DD5-DD10, где операнды

[А] и [В] из прямого кода преобразуются в обратно модифицированный код ( в

знаковой области поятся второй разряд и число будет 11 разрядное с 2 разрядами

в знаковой части ).

Далее операнды поступают

на сумматор в обратно модифицированном коде, реализованный тремя четырёх

разрядными АЛУ выполняющими операцию сложения (для нормальной работы сумматора

на входы Е0 и Е4 уровень логического "0", а на входы М, Е2, Е3 подаём уровень логической "1",

в случае переполнения, с выхода С0 на

вход С4 следующего АЛУ будет произведён

перенос логической "1", в противном случае "0").

Затем происходит проверка

результата в обратно модифицированном коде на наличие переноса, данный блок

реализован на элементе "искл. или", на входы подаются два разряда из

знаковой области результата, и в случае переполнения на выходе будет уровень

логической "1", в противном случае "0".

Далее результат в обратно

модифицированном коде попадает в преобразователь кода, который построен по

такой же технологии что и преобразователь кода описанный ранее.

Далее результат в прямом

коде поступает на входы десяти разрядного регистра Рг3 реализованном как

сказано выше, на двух восьми разрядных регистрах, с управляющим сигналом CS3.

Затем происходит

определение флагов S, P, Z:

Флаг Z – реализован на 3 элементах "3ИЛИ-НЕ"

объединённых в один корпус и 1 элементом "3И-НЕ" и 1 элементе "НЕ".

Флаг P - реализован на 6 элементах "искл.

или" и 1 элементе "НЕ".

Флаг S – это знак результата.

Эти данные вносятся в

четырёх разрядный регистр флагов с управляющим сигналом CS3.

5. Расчетная часть

В данном разделе

выполняется расчет:

-

времени

выполнения операции в разработанном блоке;

-

мощности

потребляемой блоком;

-

параметров

надежности блока.

5.1 Расчет времени выполнения

операции в БСДЧСПЗ

Основой для расчета

послужили:

1. Схема электрическая принципиальная.

2. Таблица 2. Параметры микросхем.

3. Временные диаграммы, разработанные

для схемы электрической функциональной.

4. Формулы, выведенные для проведенных

ВД.

Время срабатывания для

схемы электрической функциональной определяется по формуле:

t1= τзад.Рг1 = 30,5 [нс]

t2 = τзад.Рг2+τзад.ЛП5+ τзад.,DD11 + τзад.DD121 + τзад.DD13 + τзад.,Лп5 =

= 30,5 + 27,5+50+50+50+27,5

= 235,5 [нс]

t3 = τзад.Рг3 + τзад.ЛП5(DD21) + τзад.ЛП5(DD22) + τзад.ЛП5(DD22) + τзад.ЛП5(DD22) +

+τзад.ЛН1 =30,5+27,5+27,5+27,5+27,5+8,5 = 149

[нс]

t4 = τзад.Рг4 = 30,5 [нс]

Tвып.операции = t1 + t2 + t3 + τ4=30,5+205+149+30,5=

445,5 [нс]

5.2

Расчёт потребляемой мощности

Рпотр ИР13

= 0,116*5 = 0,58 Вт

Рпотр ЛП5

= 0,05*5 = 0,25 Вт

Рпотр ИП3

= 0,15*5 = 0,75 Вт

Рпотр ЛЕ4

= 0,068*5= 0,034 Вт

Рпотр ЛА4

= 0,0165*5 = 0,082 Вт

Рпотр ЛН1

= 0,033*5 = 0,165 Вт

Рпотр ИР13

= 0,116*5 *7= 4,06 Вт

Рпотр ЛП5

= 0,05*5*12 = 3 Вт

Рпотр ИП3

= 0,15*5*3= 2,25 Вт

Рпотр ЛЕ4

= 0,068*5*1 = 0,034 Вт

Рпотр ЛА4

= 0,0165*5*1 = 0,082 Вт

Рпотр ЛН1

= 0,033*5*1 = 0,165 Вт

Рпотр

БСДЧфз = 4,06+3+2,25+0,034+0,082+0,165 = 9,5 Вт

5.3

Расчёт параметров надёжности

Надёжность - это

комплексное свойство машин, технических устройств, систем, приборов,

заключающееся в его способности выполнять заданные функции, сохраняя при этом

свои характеристики при определённых условиях эксплуатации, в установленных

пределах.

Критерии

надёжности:

Р(t) = е-λΣ*t

2. Интенсивность

отказов - это отношение числа отказавших изделий в единицу времени к среднему

числу изделий, исправно работающих в данный отрезок времени.

3. Вероятность

отказа - это вероятность того, что при определённых условиях эксплуатации, в

заданном интервале времени произойдёт хотя бы один отказ.

Q(t) = 1 - P(t)

4. Среднее время

наработки до первого отказа.

Тср = 1/ λΣ

Таблица

3: Данные о составе элементной базы схемы электрической принципиальной

|

Наименование и тип элемента

|

Обозначение по схеме Э3

|

Кол-во элементов Ni

|

Интенсивность отказов λi*10-6 ч-1

|

Ni* λi*

10-6 ч -1

|

|

Микросхема ИР13

|

DD1-DD4,

DD19-DD20,

DD25

|

7

|

0,1

|

0,7

|

|

Микросхема ЛП5

|

DD5-DD10,

DD15-DD18,

DD21-DD22,

|

12

|

0,1

|

1,2

|

|

Микросхема ИП3

|

DD1-DD13

|

3

|

0,1

|

0,3

|

|

Микросхема ЛЕ4

|

DD23

|

1

|

0,1

|

0,1

|

|

Микросхема ЛА4

|

DD24

|

1

|

0,1

|

01

|

|

Микросхема ЛН1

|

DD14

|

1

|

0,1

|

0,1

|

|

Резистор

|

R1

|

1

|

0,1

|

0,1

|

|

Разъём

|

Х1

|

1

|

0,1

|

0,1

|

λΣ

= 2.7*10-6 ч-1

P(10)

= ℮-2.7*10‾5 = 0,999

P(1000)

= ℮-2.7*10‾3 =0,997

P(10000)

℮-2.7*10‾2 =0,973

P(50000)

℮-2.7*5*10‾2 =0,874

P(100000)

℮-2.7*10‾1 =0,764

P(200000)

℮-2.7*2*10‾1 =0,584

P(236407)

℮-2.7*0.236407 =0,530

Определение

вероятности безотказной работы:

Рисунок: График

вероятности безотказной работы.

Определение

вероятности отказа:

Q(10)

= 1 - 0,999 = 0,001

Q(1000)

= 1 - 0,997 = 0,003

Q(10000)

= 1 - 0,973 = 0,027

Q(50000) = 1 - 0,874 = 0,126

Q(100000)

= 1 - 0,764 = 0,236

Q(200000) = 1 - 0,584 = 0,416

Q(236407) = 1 - 0,530 = 0,470

Рисунок: График

вероятности отказа.

Определение

среднего времени наработки до первого отказа:

Тср = 1/ λΣ = ½.7*10-6 ≈ 370370,370

ч