Схемы для внешнего устройства

Эксплуатация

средств ВТ

КОМПЛЕКТ СХЕМ ДЛЯ

ВНЕШНЕГО УСТРОЙСТВА.

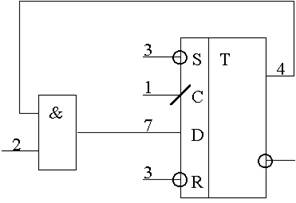

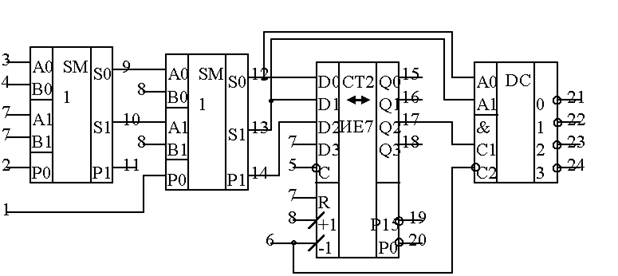

1.D-триггер с обратной связью и динамическим

управлением.

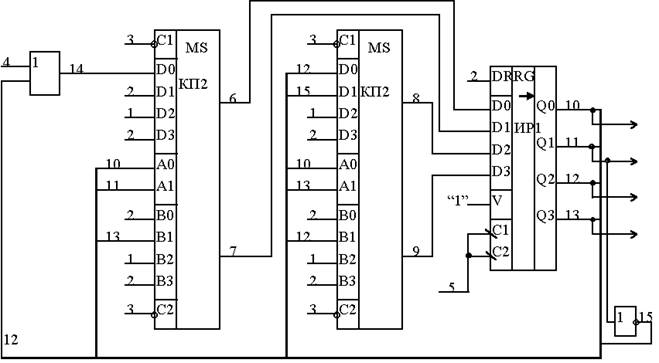

2.Схема синхронного цифрового автомата.

3.Последовательностная схема,которая с приходом стартового

сигнала А=1 под действием синхроимпульсов СИ принимает последовательно

состояния: 000-исходное состояние, 001, 100, 101, 100, 010, 011, 000...

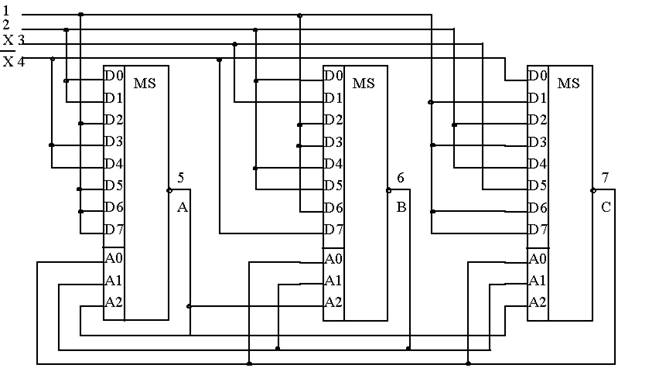

4.Aсинхронная последовательностная схема ,кoтopaя пoд

дeйcтвиeм cигнaлoв, пocтупaющиx нa вxoд X(X), пpинимaeт пocлeдoвaтeльнo кoдoвыe

cocтoяния ABC: 000, 001, 011, 111, 101, 100, 000.

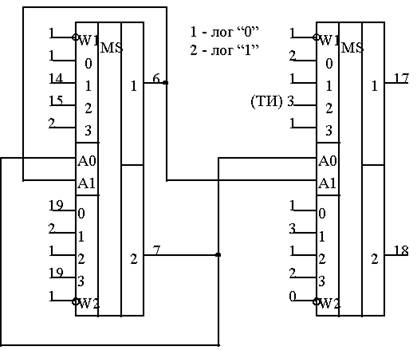

5.Схема содержит цифровой автомат на мультиплексоре 1

с циклической последовательностью состояний АВ=(00,01,11,10) и комбинационную

логику на мультиплексоре 2, выходные сигналы которой зависят от состояний

автомата и тактовых сигналов на входе 3

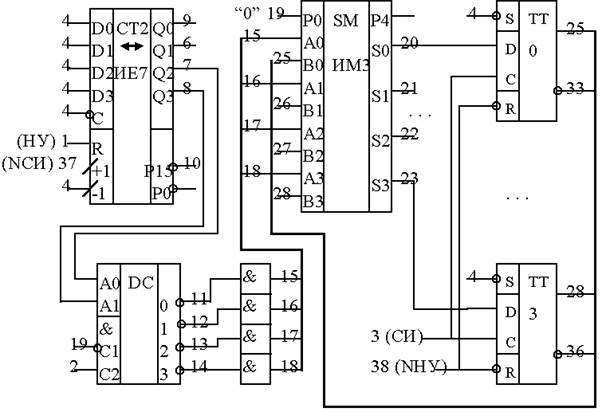

6.Схема, однократно вырабатывающая последоватеьлность

сигналов 010011000111000011110000011111 в виде импульсов (выход 24) или

потенциалов (выход 22). Сигнал начальной установки поступает на вход 2,

синхроимпульсы - на вход 1.

7.Схема, которая на одном их выходов дешифратора

вырабатывает непрерывную серию импульсов.Номер выхода и число импульсов в серии

зависят от числа "1" на входах 1,2,3,4.

8.Схема, подсчитывающая сумму S= p(i)*c(i)*X по mod

16.

X-сигнал на входе .. , p(i)-весовой коэффициент i-го

синхроимпульса на входе ...

Веса p(1-4)=1, p(5-8)=2, p(9- 12)=4, p(13-16)=8

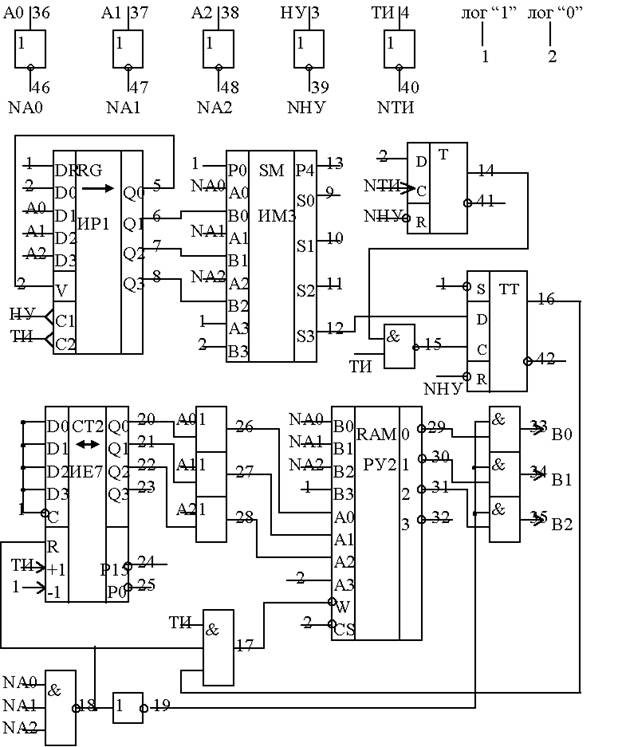

9.Схема, выполняющая транспонирование квадратной

матрицы 4*4 однобитовых элементов. Исходная матрица размещена в ячейках 0,1,2,3

RAM-1. Транспонированная матрица размещается в RAM-2.

10.Сxeмa цифpoвoгo уcтpoйcтвa для oбpaбoтки N

3-paзpядныx кoдoв, oтличныx oт 0 и нe paвныx мeжду coбoй, пocлeдoвaтeльнo

пocтупaющиx нa А-входы.

Aлгopитмoм oбpaбoтки пpeдуcмoтpeнo: фикcaция A(1) в

peгиcтpe; cpaвнeниe A(i) c A(1); зaпиcь инверсного кода A(i+1) в ячeйку ЗУ пo

aдpecу A(i+1),если A(i)>A(1); пocлeдoвaтeльный вывoд coдepжимoгo ячeeк ЗУ нa

выходы B пocлe пpиeмa A-кoдoв. (i=2,3...N-1)

11.Данные, хранимые в ячейках ЗУ, представляют

положительные и отрицательные числа в дополнительном коде с одним знаковым

разрядом. Схема уменьшает содержимое ячеек 1,2,...8, начиная с ячейки 1, на

величину разности /S[i]-S[i-1]/, где S[i],S[i-1]- количество "1"

соответственно в текущем и предшествующем адресном коде при условии,если его

можно редставить в 4-разрядной сетке (без переполнения),

(i-1),i-последовательные номера ячеек.

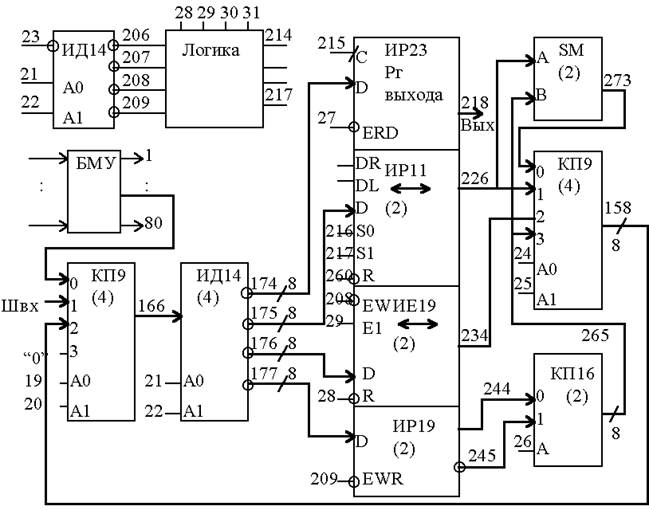

12.Схема блока обработки данных с микропрограммным

управлением.