Система керування складом готової продукції

Міністерство

освіти і науки України

Факультет

інформаційних технологій

Кафедра

комп’ютерних систем та мереж

КУРСОВА

РОБОТА

з

дисципліни «Технології проектування комп’ютерних систем»

на

тему: «Система керування складом готової продукції»

РЕФЕРАТ

Пояснювальна записка: сторінок, рисунків, таблиць,

використаних джерел.

Об’єкт аналізу - системна програма керування складом готової

продукції в осередку Active-HDLта її проектування.

Робота складається з чотирьох розділів.

Перший розділ присвячений ознайомленню з мовою VHDL, її перевагам та недолікам, а також

огляду та опису функціонування системи керування складом готової продукції.

У другому розділі виконаний аналіз, опис та побудова

асинхронного RS-тригера, що відповідає роботі даної

системи.RS-тригер побудований на

логічних елементах.

Третій розділ присвячений розробці та реалізації діаграми

станів кінцевого автомату, що відповідає функціонуванню системи керування

складом.

ЗМІСТ

1. АЛГОРИТМ

ФУНКЦІОНУВАННЯ ПРИСТРОЮ

.1 Постановка

задачі

.2 Опис принципу

дії пристрою

. РОЗРОБКА

СХЕМ ТА ПРОГРАМ ПРИМІТИВНИХ КОМПОНЕНТІВ ЦИФРОВОГО АВТОМАТУ

.1 Розробка

перетворювача логічного синтезу

. РОЗРОБКА

БЛОК-СХЕМИ ТА ДІАГРАМИ СТАНІВ РОБОТИ ПРИСТРОЮ

. ТЕСТУВАННЯ

РОБОТИ ПРИСТРОЮ ТА АНАЛІЗ ЧАСОВИХ ДІАГРАМ

ВИСНОВКИ

СПИСОК

ВИКОРИСТАНИХ ДЖЕРЕЛ

1. АЛГОРИТМ

ФУНКЦІОНУВАННЯ ПРИСТРОЮ

1.1 Постановка задачі

Метою даної курсової роботи є проектування та написання

програми для функціональної системи, що керує складом готової продукції.

Комп’ютерні технології не стоять на місці, щодня, щохвилини

вони розвиваються, набуваючи все нових та нових можливостей. Ще декілька

десятків років тому комп’ютер могли придбати лише великі підприємства, оскільки

він був дуже громіздким, займав багато місця та на його придбання підприємства

витрачали великі кошти. Проте сьогодні комп’ютер є майже в кожної людини.

Основним завданням комп’ютерних технологій є впровадження

функцій, які полегшують життя кожного. І дійсно, на сьогоднішній день важко

уявити повсякденне життя без підприємств, супермаркетів, банків та інших

галузей, де відбувається тісна взаємодія людини з технікою. Комп’ютери стали

невід’ємною частиною нашої роботи, дозвілля та надійним джерелом інформації.

Саме тому написання програми для автоматизації функціонування

системи керування складом готової продукції є актуальним на сьогоднішній час.

Під системою керування складом готової продукції мається на увазі

автоматизоване підприємство, яке займається прийомом, зберіганням та доставкою

певної продукції. Дуже важливо, щоб усі ці процеси виконувались чітко та

своєчасно. Забезпечити повну та безвідмовну роботу усієї системи можна,

спроектувавши та застосувавши програму керування системою.

В якості осередку написання програми було обрано Active-HDL 9.1.

Стандартні мови опису апаратури(VHDLіVerilog) дуже зручні для

проектування електроннихсистем і пристроїв на основі ПЛІС і зростають у

популярності. При проектуванні складних ПЛІС інженери вже не можуть

використовувати булеві рівняння або описи у вигляді логічних схем, щоб

забезпечити швидке та ефективне повнепроектування. Мови опису апаратури типу

VHDL (Very high speed integrated circuit Hardware Description Language)

забезпечуютьвисокорівневий опис найскладніших пристроїв, дозволяють виконати

проектування значно швидше, підтримують створення бібліотекпроектування,вякихкомпонентиможутьбутибагаторазововикористанівподальшихпроектах.

До сих пір одним з найбільш трудомістких етапів проектування

пристроїв є створення електричних схем. Це пов'язано з тим, що безліч

електронних компонентів і зв'язків між ними доводиться вводити вручну. Після

завершення схеми багато часу займає перевірка правильності схеми. САПР (системи

автоматизованого проектування) поліпшили ситуацію, але і вони також віднімають

багато часу на верифікацію проектів. Модернізація таких схем часто стає просто

неможливою без тотального перероблення конструкції друкованої плати. Сучасність

вимагає, щоб схеми були описані чітко і ємко. Саме тому три десятиліття тому

при проектуванні НВІС (Над великих інтегральних схем) від створення логічних схем

стали відмовлятися. Дійсно, доходило до того, що електрична схема кристала

розміром 1х1 см займала кілька тисяч аркушів формату A3.

Мова VHDL - незвична мову, як для програмістів, так і для

розробників електронної апаратури. Це пов'язано з тим, що за своєю суттю VHDL -

мова паралельного програмування.

Слід врахувати, що сучасна технологія проектування логічних

схем пред'являє до проектів, описаним на VHDL, цілий ряд особливих вимог. А

схемотехнік, який все-таки вирішив вивчити VDHL, з цими особливими вимогами

часто не знайомиться.

Проте VHDL-програми мають переваги перед схемним

проектуванням:

за допомогою VHDL набагато простіше ввести і перевірити

великий проект. Десятьма рядками VHDL можна описати як один, так і 100 000

тригерів;

VHDL-проекти не обов'язково макетувати. Достатньо просто

запустити їх VHDL-код через симулятор HDL;

VHDL-програми не вимагають їх подання у вигляді схеми.

Нечіткість і недбалість опису також виключаються, так як таку програму не

складно перевірити;

VHDL-програми надійні. Синтаксичний аналіз, програмне

моделювання та компіляція в логічну схему швидко виявляють помилки проекту;

VHDL-програми універсальні. Однократно розроблений

VHDL-компонент може бути багато разів використаний в безлічі інших проектів.

При цьому функції і параметри компонента можна підлаштовувати під нові завдання

на будь-якому етапі проектування. Також універсальність полягає в тому, що VHDL

проекти з однієї елементної бази легко переносяться на іншу (наприклад,

мікросхеми різних технологій);

VHDL-код довговічний, на відміну від електричної схеми, яка

завжди розробляється під конкретну елементну базу. Оскільки зазвичай через 3-5

років елементна база змінюється, змінюються й електричні схеми, що

використовують її. Хороше технічне рішення на мові VHDL може бути використано

на протязі десятиліть.

Недолік VHDL-програм:

на Заході найбільше поширення отримала мова Verilog. Два

десятиліття тому ця мова випереджувала інші HDL мови завдяки тому, що займала

мало обчислювальних ресурсів комп'ютера. VHDL - більш універсальнаі швидка

мова, але вона програвала у швидкодії мові Verilog, особливо при моделюванні на

рівні вентилів.

Програма Active-HDL 9.1 не має особливих вимог до

комплектуючих комп’ютера, на якому вона буде працювати, окрім об’єму пам’яті.

Наведемо деякі характеристики комп’ютера:

Таблиця 1.1 - Характеристики комп’ютера

|

Процесор

|

AMD Athlontm

64 Processor

|

|

Частота

|

2 GHz

|

|

Швидкість

|

628 MGz

|

|

Материнська плата

|

K8NF4G-SATA2

|

|

ОЗП

|

1 Gb

|

|

Жорсткий диск

|

ST9500325AS

(S2W0FRTD)

|

|

Мережева карта

|

Будь-яка

|

|

Монітор

|

Будь-який

|

1.2 Опис принципу дії пристрою

асинхронний тригер склад продукція

Даний пристрій являтиме собою кінцевий автомат Мілі.

Автомат - це дискретний перетворювач інформації, що здатний

приймати різні стани, переходити під дією вхідних сигналів із одного стану в інший

та видавати вихідні сигнали.

Кінцевий - це автомат із кінцевою множиною станів, а також

вхідних і вихідних сигналів.

Стан - це передісторія автомату.

Математичною моделлю реального кінцевого автомату є

абстрактний автомат, який можна представити у вигляді:

Рис. 1.1 -Модель кінцевого автомату

Дискретний проміжок часу функціонування автомату називається

тактом. В залежності від довжини такту автомати бувають синхронного типу та

асинхронного.

Принцип роботи автомату: в кожний момент часу він знаходиться

в деякому стані a(t) із усієї множини станів,

початковому моменту часу t=0стан автомату відповідає a0.В деякий момент часу tавтомат сприймає вхідний сигнал x(t),видає вихідний сигнал y(t) та переходить в наступний стан a(t+1).

Особливістю автомату Мілі є те, що його вихідні сигнали

залежать як від стану автомату, так і від значень вхідних сигналів.

В автоматі Мура вихідні сигнали в кожний дискретний момент

часу залежить тільки від внутрішнього стану автомату і не залежить від вхідних

сигналів.

Побудуємо модель кінцевого автомату Мілі, яка описуватиме

функціонування даного складу готової продукції.

Рис. 1.2 - Модель кінцевого автомату Мілі для функціонування

складу готової продукції

В даному випадку:

х1, х2, х3 - вхідні сигнали, тобто тип продукції, що

поступила до складу (х1 - одяг, х2 - взуття, х3 - продукти);

у1, у2, у3 - вихідні сигнали, тобто склад, куди необхідно

транспортувати готову продукцію (у1 - магазин 1 (туди поставляються одяг та

взуття), у2 - магазин 2 (одяг та взуття), у3 - магазин 3 (супермаркет, туди

поставляються продукти та одяг));

а1, а2, а3 - внутрішні стани складу, тобто тип роботи, який

проводиться з даною продукцією (а1 - сортування одягу на пори року, а2 -

сортування на чоловіче та жіноче, а3 - безпосереднє вантаження до вантажівок).

В залежності від того, який тип продукції поступив до складу,

за допомогою спеціальної таблиці переходів визначається стан автомату у даний

момент часу, та формується сигнал на його виході, тобто транспортування у

відповідний магазин.

Побудуємо таблицю функціонування кінцевого автомату Мілі.

Таблиця 1.2 - Таблиця станів кінцевого автомату

|

Вхідні сигнали

|

Стани

|

|

а1

|

а2

|

а3

|

|

х1

|

а2

|

а3

|

а1

|

|

х2

|

а1

|

а3

|

-

|

|

х3

|

-

|

-

|

а3

|

|

Вихідні сигнали

|

у1

|

у2

|

у3

|

2. РОЗРОБКА СХЕМ ТА ПРОГРАМ ПРИМІТИВНИХ КОМПОНЕНТІВ ЦИФРОВОГО

АВТОМАТУ

2.1 Розробка перетворювача логічного синтезу

Під розробкою перетворювача логічного синтезу розуміється

побудова майбутнього пристрою за допомогою тригерів. Автомат Мілі представляє

собою роботу асинхронного RS-тригера.

Тригер - це електронний пристрій, що призначений для запису

та зберігання інформації. Зазвичай він має два виходи - прямий та інверсний, а

також деяку кількість входів, в залежності від поставленої задачі. Під дією

вхідних сигналів змінюються стани виходів. Для виготовлення тригерів зазвичай

використовуються біполярні уніполярні транзистори (напівпровідникові прилади).

Тригер - логічний пристрій, здатний зберігати 1 біт даних.

Тригер є основним компонентом більш складних пристроїв, таких як лічильники,

зсувні регістри і регістри пам'яті.

Інформація може записуватися в тригери вільно (безперервно),

тобто при подачі сигналів на вхід, стан виходу змінюється в реальному часі. Такі

тригери називаються асинхронними. А інформація може записуватися, тільки коли

активний синхронізуючий сигнал, за відсутності позитивного рівня напрузі на

ньому; інформація на виходах змінитися не може - синхронні (тактовані)

тригери.тригер називається так через назви його входів: R - reset (скинути) і

S-set (встановити). Він оснащений двома входами і двома виходами: Q-прямий

вихід; і  - інверсний.

- інверсний.

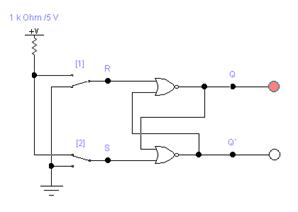

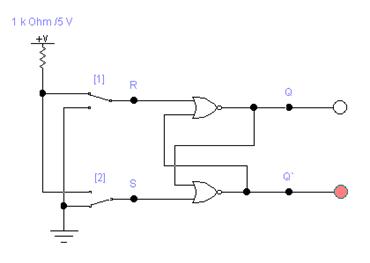

У середовищі ElectronicsWorkbenchреалізуємо асинхронний RS-тригер на основі логічних

елементів 2АБО-НІ.

Рис. 2.1 - Асинхронний RS-тригер на логічних елементах

2АБО-НІ

Розглянемо принцип роботи даного тригеру.

В нульовий момент часу, коли на жоден вхід (R і S) не подали

логічну одиницю, прямий вихід Q = 0, інверсний, відповідно, = 1. Якщо на вхід S подати напругу,

рівень якої відповідатиме одиниці, то вихід Q стрибкоподібно змінить своє

значення на 1, а

= 1. Якщо на вхід S подати напругу,

рівень якої відповідатиме одиниці, то вихід Q стрибкоподібно змінить своє

значення на 1, а  на 0. В даному випадку відбудеться запис інформації. Якщо

прибрати одиницю з "Set", тоді виходи не змінять свій стан,

залишаться такими, якими були - прояв властивості пам'яті. При подачі

позитивного сигналу на вхід скидання, тобто R = 1, інверсний вихід різко стане

дорівнювати 1, а прямий Q - 0. У роботітригера є недолік: існує заборонена

комбінація. Не можна одночасно подавати поодинокі сигнали на обидва входи,

нормальна робота тригера в цьому випадку неможлива.

на 0. В даному випадку відбудеться запис інформації. Якщо

прибрати одиницю з "Set", тоді виходи не змінять свій стан,

залишаться такими, якими були - прояв властивості пам'яті. При подачі

позитивного сигналу на вхід скидання, тобто R = 1, інверсний вихід різко стане

дорівнювати 1, а прямий Q - 0. У роботітригера є недолік: існує заборонена

комбінація. Не можна одночасно подавати поодинокі сигнали на обидва входи,

нормальна робота тригера в цьому випадку неможлива.

Рис. 2.2 - Робота тригера при R = 0, S = 1

Рис. 2.3 - Робота тригера при R = 1, S = 0

Згідно вище описаному принципу роботи тригера побудуємо

таблицю істинності.

Таблиця 2.1 - Таблиця істинності тригера

|

R

|

S

|

Q(t)

|

Q(t+1)

|

Опис

|

|

0

|

0

|

0

|

0

|

Зберігання

інформації

|

|

0

|

0

|

1

|

1

|

|

|

0

|

1

|

0

|

1

|

Установка “1”

|

|

0

|

1

|

1

|

|

|

1

|

0

|

0

|

0

|

Установка “0”

|

|

1

|

0

|

1

|

0

|

|

|

1

|

1

|

0

|

*

|

Заборонена

комбінація

|

|

1

|

1

|

1

|

*

|

|

* - неможливий стан

Реалізуємо RS-тригер у середовищі Active-HDL та складемо його структурний опис.

Оскільки у вбудованій бібліотеці VHDL немає елемента RS-тригер, його треба

створити. Для початку створимо та пропишемо лістинг логічних елементів: АБО-НІ

та НІ.

Лістинг елемента АБО-НІ:IEEE;IEEE.STD_LOGIC_1164.all;abo_ni

is(: in STD_LOGIC;: in STD_LOGIC;: out STD_LOGIC

);abo_ni;abo_ni of abo_ni is<= not(x1 or x2) after 2

ns;abo_ni;

Лістинг елемента НІ:IEEE;IEEE.STD_LOGIC_1164.all;ni is(: in

STD_LOGIC;: out STD_LOGIC

);ni;ni of ni is<= not x after 2 ns;ni;

Зберігаємо дані файли та компілюємо.

Далі створюємо новий файл Blockdiagram, на якому позначаємо входи та вихід

майбутнього RS-тригера.

Створені щойно елементи з’явились в даному робочому просторі,

які можна побачити на панелі інструментів ShowSymbolsToolbox (S).

Блок-діаграма RS-тригера має вигляд:

Рис. 2.4 - RS-тригер, спроектований у програмі VHDL

Таблиця 2.2 - Таблиця функціонування тригера

Символ N означає незмінне (попереднє) значення сигналу, через “-” позначено будь-яке із значень

сигналу (0, 1).

Згідно таблиці функціонування тригера складемо його

алгоритмічний опис. Для цього використаємо оператор

process.IEEE;IEEE.STD_LOGIC_1164.all;RS_trigger2 is(: in STD_LOGIC;: in

STD_LOGIC;: out STD_LOGIC

);RS_trigger2;RS_trigger2 of RS_trigger2 is(R,S)R='0'if

S='0'Q <= S;if;S='1'Q <= '0';if;if;R='1'Q <=

'1';if;process;RS_trigger2;

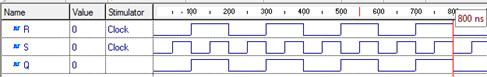

Побудуємо часову діаграму роботи тригера, реалізованого при

структурному описі. Пункт меню Simulation →Initializesimulation →Newwaveform.Перетаскуємо на робочу область

ініціалізований файл, згідно якого побудується часова діаграма.

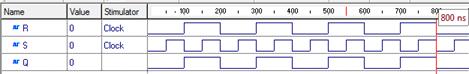

Задаємо частоту вхідних сигналів R та S. На діаграмі NET66 та NET90 - елементи АБО-НІ та НІ, які були

створені в ході програми.

Натискаємо кнопку RunFor (F5) для

побудови часової діаграми.

Рис. 2.5 - Часова діаграма роботи тригера

Зафарбовані сірим кольором переходи на виході Q означають невизначені стани (згідно

таблиці функціонування тригера).

Побудуємо часову діаграму роботи тригера, реалізованого при алгоритмічному

описі.

Рис. 2.6 - Часова діаграма роботи тригера

В даному розділі була проведена розробка перетворювача

логічного синтезу, а саме RS-тригера. Виконаний структурний та алгоритмічний

опис пристрою, побудовані його часові діаграми, які відповідають заданій

таблиці функціонування. Також виконана реалізація даного елементу в середовищі ElectronicsWorkbench, описаний принцип роботи

схеми.

3. РОЗРОБКА БЛОК-СХЕМИ ТА ДІАГРАМИ СТАНІВ РОБОТИ ПРИСТРОЮ

Реалізуємо роботу системи керування складом готової продукції

за допомогою діаграми станів. Діаграма станів будується в програмі Active-HDL.

Оскільки створюється нова діаграма станів, для неї необхідно

створити свій власний файл бібліотеки, в який включити інформації щодо входів,

виходів та станів даної системи.

Створюємо звичайний файл vhdl-source під назвою my_type, в який вписуємо

наступний лістинг:my_type istype1 is (x1, x2, x3);--vhodutype2 is (y1, y2,

y3);--vіhodumy_type;

Зберігаємо файл (Ctrl+S) та

компілюємо його (F11).Після

компіляції біля імені повинна з’явитися зелена галочка - це означає, що

компіляція пройшла успішно й помилки не виявлені.

Рис. 3.1 - Успішна компіляція

Далі створений щойно файл треба підключити до загальних

бібліотек. На створеному файлі діаграми станів угорі можна спостерігати надпис,

на якому натиснути правою кнопкою миші та в контекстному меню обрати

Властивості.

Рис. 3.2 - Контекстне меню файлу діаграми станів

У вкладці DesignUnitHeaderвідкритого вікна CodeGenerationSettingsокрім існуючих бібліотек прописуємо

нещодавно створену.

Тепер програма остаточно готова до роботи.

Задаємо входи х, Reset, синхровхід clkта вихід y.

Рис. 3.4 - Входи та вихід діаграми

Для побудови діаграми станів потрібно застосувати стани

(зелені кола) та переходи між ними (стрілки). У властивостях кожної стрілки (її

контекстне меню) задається умова переходу з одного стану в інший.

Рис. 3.5 - Задання умови переходу

Рис. 3.6 - Задання умови переходу

У полі Conditionзадаємо умову переходу (при якому значенні вхідного сигналу

здійсниться перехід), а в полі Action вписуємо дію, яка виконається при виконанні заданої умови

(значення перейде до певного виходу).

Аналогічно задаємо умови переходу для всієї діаграми станів.

Готова діаграма має вигляд:

Рис. 3.7 - Діаграма станів системи керування складом готової

продукції

Далі у властивостях входів та виходів необхідно задати

кожному відповідний тип, який раніше було прописано в бібліотеці.

Рис. 3.8 - Завдання типу входів та виходів

В даному розділі була реалізована робота системи керування

складом готової продукції за допомогою діаграми станів. Діаграма побудована на

основі таблиці станів кінцевого автомату Мілі, складеної в першому розділі.

4. ТЕСТУВАННЯ РОБОТИ ПРИСТРОЮ ТА АНАЛІЗ ЧАСОВИХ ДІАГРАМ

Побудуємо часову діаграму роботи тригера, реалізованого при

структурному описі. Пункт меню Simulation →Initializesimulation →Newwaveform.Перетаскуємо на робочу область

ініціалізований файл, згідно якого побудується часова діаграма.

Задаємо частоту вхідних сигналів R та S. На діаграмі NET66 та NET90 - елементи АБО-НІ та НІ, які були

створені в ході програми.

Натискаємо кнопку RunFor (F5) для

побудови часової діаграми.

Рис. 4.1 - Часова діаграма роботи

тригера

Зафарбовані сірим кольором переходи на виході Q означають невизначені стани (згідно

таблиці функціонування тригера).

Побудуємо часову діаграму роботи тригера, реалізованого при

алгоритмічному описі.

Рис. 4.2 - Часова діаграма роботи

тригера

ВИСНОВКИ

В ході виконання курсової роботи було спроектовано та

написано програму для функціональної системи, що керує складом готової

продукції.

Було виконано такі етапи:

ознайомлення з мовою VHDL, її перевагам та недолікам,

а також огляду та опису функціонування системи керування складом готової

продукції.

виконаний аналіз, опис та побудова асинхронного

RS-тригера, що відповідає роботі даної системи. RS-тригер побудований на

логічних елементах.

розробка та реалізація діаграми станів кінцевого

автомату, що відповідає функціонуванню системи керування складом.

СПИСОК ВИКОРИСТАНИХ ДЖЕРЕЛ

1. Алексенко

А.Г., Шагурин П.И. Микросхемотехника: Учеб. пособие для вузов. - М.: Радио и

связь, 1990, - 496 с.

2. Бабич

М.П., Жуков І. А. Комп'ютерна схемотехніка. Навч. посібник. - К.: НАУ, 2002. -

508 с.

3. Горошков

Б. И. Радиоэлектронные устройства: Справочник / Б. И. Горошков. - М.: Радио и

связь, 1984. - 400 с.

4. Генератор

импульсов прямоугольной формы [Електронний ресурс] - Режим доступу:

http://edu.dvgups.ru/METDOC/GDTRAN/YAT/TELECOMM/METR_SERT/METOD/LAB_2/frame/2.htm.

5. Бибило

П.Н. Основы языка VHDL. - Мінськ:

Ин-т техн. кибернетики НАН Беларуси, 1999. - 202 с. - ISBN 985-6453-30-5.