|

|

|

|

|

|

1

|

1

|

|

|

|

1

|

0

|

1

|

0

|

|

0

|

1

|

0

|

|

0

|

0

|

Неопределённое

состояние

|

Не разрешается

одновременная подача напряжения низкого уровня на оба входа  -триггера. Триггер типа RS, как и

-триггера. Триггер типа RS, как и  -триггер, "запоминает", на какой из двух входов (R или

S) поступил последний сигнал: если на вход R, триггер находится в нулевом

состоянии (Q = 0 и

-триггер, "запоминает", на какой из двух входов (R или

S) поступил последний сигнал: если на вход R, триггер находится в нулевом

состоянии (Q = 0 и = 1), а

если на вход S, то в единичном состоянии (Q = 1 и

= 1), а

если на вход S, то в единичном состоянии (Q = 1 и = 0).

= 0).

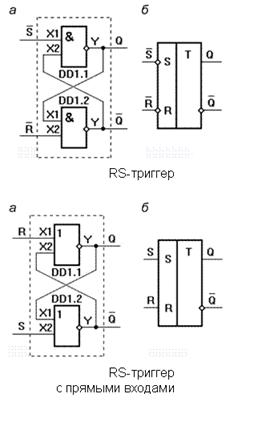

Рисунок 4.

RS-триггер: его условное графическое обозначение и схема с четырьмя логическими

элементами И-НЕ.

На рисунке 4

показана схема RS-триггера, выполненного на логических элементах И-НЕ. Она

отличается от схемы  -триггера

тем, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только

обеспечивают необходимый уровень входных сигналов. [11]

-триггера

тем, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только

обеспечивают необходимый уровень входных сигналов. [11]

Изменение входных

сигналов от низкого уровня до высокого приводит к смене состояния триггера

(моменты t1, t2, t2 и t5; в момент t4 опрокидывания не происходит, так как

триггер уже установлен в единичное состояние в предшествующий момент - t3,

рисунок 5).

Рисунок 5.

Временная диаграмма работы RS-триггера

Все сказанное

относительно RS-триггера сохраняет силу и для  -триггера. Единственное различие касается инверсии уровней входных

сигналов (R вместо

-триггера. Единственное различие касается инверсии уровней входных

сигналов (R вместо  и S

вместо

и S

вместо ). [15; 104]

). [15; 104]

Глава 1. Цифровые устройства

последовательного типа

Цифровые устройства

последовательного типа или цифровые автоматы с памятью - это электронные

цифровые устройства, логические значения на выходах которых определяются не

только совокупностью логических сигналов на входах в данный момент времени, но

и состоянием внутренних элементов памяти по результатам его предшествующей

работы. Запоминание предшествующих состояний выполняется при помощи триггеров и

регистров памяти.

Типичными примерами логических

автоматов с памятью являются счётчики импульсов и сдвиговые регистры [4; 113]

1.1 Общее представление о триггерах

Триггеры - это электронные

устройства, обладающие двумя устойчивыми состояниями равновесия и способные

скачком переходить из одного устойчивого состояния в другое под воздействием

внешних управляющих сигналов.

Состояние называется устойчивым,

если слабое внешнее воздействие не нарушает этого состояния. Для перехода

триггера из одного состояния в другое необходимо, чтобы входной сигнал превысил

пороговое значение.

Триггер снабжается двумя выходами:

прямым Q и инверсным Q. Состояние триггера определяет логический уровень на выходе Q. Триггеры могут иметь входы

различного типа:

R (от англ. RESET) - раздельный вход установки в состояние 0;

S (от англ. SET) - раздельный вход установки в состояние 1;

К - вход установки универсального

триггера в состояние 0;

J - вход установки универсального триггера в состояние 1;

V - вход разрешения;

С - синхронизирующий вход;

D- информационный вход;

Т - счетный вход

Обычно название триггера дают по

имеющимся у него входам:RS-триггер, JK-триггер, D-триггер и др. По способу записи информации триггеры

подразделяются на асинхронные и синхронные. Васинхронных триггерахсостояние на

выходе изменяется сразу же после изменения сигнала на информационных входах.

Всинхронных триггерахдля передачи сигнала с информационных входов на выходы

требуется специальный синхронизирующий импульс. Синхронные триггеры

подразделяются на триггеры со статическим управлением и триггеры с динамическим

управлением. В триггерах с динамическим управлением передача сигнала с

информационных входов на выходы осуществляется по фронту или по спаду

синхронизирующего импульса.

Триггеры относятся к цифровым

автоматам. В отличие от комбинационных схем состояние на выходе триггера в

данный момент времени определяется не только состояниями на входах триггера в

этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы

к которым относятся триггеры, иногда называют последовательными схемами.

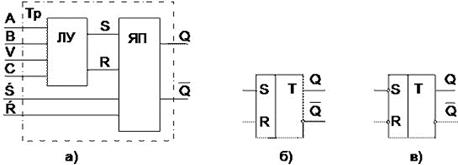

Триггеры можно представить как

устройство, состоящее из ячейки памяти ЯП и логического устройства (ЛУ)

управления, преобразующего входную информацию в комбинацию сигналов, под

воздействием которых ЯП принимает одно из двух устойчивых состояний.

Информационные сигналы поступают на

входы A и В ЛУ и преобразуются в сигналы, поступающие на внутренние входы S и R

ЯП. Процесс преобразования информационных сигналов осуществляется под

воздействием сигналов, подаваемых на вход V разрешения приёма информации и вход

C синхронизации, обеспечивающей тактируемый приём информации.

Рисунок 5

Рисунок 6

а) Обобщённое устройство триггера;

б) RS-триггер с прямыми

входами;

в) Инверсными статическими входами

При наличии входа C триггер называют

синхронным, а при его отсутствии-асинхронным. Управляющие сигналы на асинхронный

триггер воздействуют непосредственно с началом своего появления на их входах, а

в синхронных - только с приходом сигнала на входе C.

Триггеры могут иметь статические или

динамические входы. Как статические, так и динамические входы могут быть прямыми

или инверсными.

Входы называются статическими, если

они имеют непосредственную связь с источником входных сигналов. Сигналом для

управления статическим триггером с прямыми статическими входами является

уровень лог «1», а для управления триггером с инверсными входами - уровень лог

«0».

Входы называются динамическими, если

они соединены с источником входных сигналов через развязывающие цепи:

магнитные, электронные или RC-цепи. Они реагируют только на перепады входных

сигналов. Если срабатывание триггера происходит при изменении входного сигнала

от «0» к «1», то входы называются прямыми, а если при изменении сигнала от «1»

к «0», то - инверсными.

Входы Ś

и Ŕ называются входами асинхронной установки триггера. Они

предназначены для подачи приоритетных сигналов установки триггера в исходное

состояние (0 или 1) в начале цикла работы независимо от воздействия

информационных сигналов, то есть в обход схемы управления. [9; 315]

1.2 RS-триггеры

Наибольшее применение находят

триггеры с раздельным запуском, которые называются RS-триггерами. Их условное

графическое обозначение приведено на рисунке 1. В простейшем RS-триггере

информационные сигналы подаются непосредственно на входы S и R ячейки памяти.

Входы, на которые подаются

запускающие импульсы, называются установочными. Буквой S обозначают вход, на

который подаётся сигнал, устанавливающий триггер в единичное состояние (Q=1,  ). Буквой R (Reset - сброс) обозначают вход, на который подаётся

сигнал сброса, переводящий триггер в состояние «0»

). Буквой R (Reset - сброс) обозначают вход, на который подаётся

сигнал сброса, переводящий триггер в состояние «0»  . Буквой Q обозначается

прямой выход, а

. Буквой Q обозначается

прямой выход, а  -

инверсный.триггеры применяются как самостоятельно, так и в составе других более

сложных триггеров, а также входят в состав регистров и счётчиков.

-

инверсный.триггеры применяются как самостоятельно, так и в составе других более

сложных триггеров, а также входят в состав регистров и счётчиков.

1. RS-триггеры в аналогических

элементах.

Функционирование логических

устройств последовательного типа описывается таблицами переходов, которые

отличаются от таблиц истинности тем, что в них учитываются только

результативные переходы, когда изменение комбинации сигналов на входе приводит

к изменению выходного состояния. Однако таблица переходов может быть сведена к

таблице истинности, если состояние внутренних элементов памяти считать входными

сигналами.

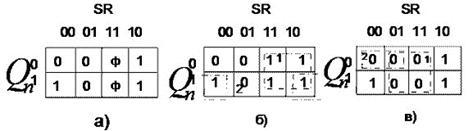

Полная таблица функционирования (таблица

истинности) приведена на рисунке 2а, в которой предыдущее состояние триггера Qn

до подачи входных сигналов является одним из входных сигналов. Выходное

состояние триггера после подачи входных сигналов обозначено символом Qn+1.

Таблица переходов триггера приведена на рисунке 7

Таблица истинности позволяет

применить рассмотренную выше методику синтеза логических устройств

комбинационного типа для синтеза устройств последовательного типа, в том числе

и RS-триггеров.

Для минимизации структурной формулы

RS-триггера заполним карту Карно, приведённую на рисунке 8.

Рисунок 7. Таблица истинности; б)

Таблица переключений RS-триггера.

Рисунок 8 Карты Карно для

минимизации структурной формулы RS-триггера

В соответствии с теорией минимизации

неопределённых логических функций, для определения прямого значения функции Qn+1

неопределённые значения карты Карно «ф» (Рисунок 3,а) заменим «1»

(Рисунок 9,б), а для определения инверсного значения  - заменим «0» (Рисунок 9,в). Для получения функции

- заменим «0» (Рисунок 9,в). Для получения функции  минимизация производится по нулям.

минимизация производится по нулям.

Минимизированные значения функций Qn+1и на элементах основного базиса имеют вид:

на элементах основного базиса имеют вид:

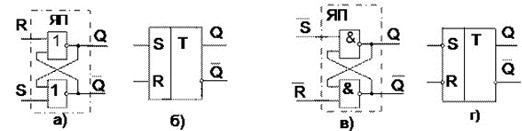

Рисунок 9. RS-триггеры:

а), б) - аналогических элементах

ИЛИ-НЕ,

в), г) - аналогических элементах

И-НЕ.

Для реализации триггера на элементах

ИЛИ-НЕ проинвертируем функцию

:

: .

.

Структурная схема триггера,

полученная в соответствии с этим выражением, приведена на рисунке44,а. В

структурной формуле установочные сигналы S и R представлены в прямом коде,

следовательно, исполнительными значениями сигналов являются уровни лог «1», то

есть триггер на элементах ИЛИ-НЕ имеет прямые статические входы.

Для реализации триггера на элементах

И-НЕ дважды проинвертируем функциюQn+1:

Как следует из полученного

выражения, исполнительными значениями сигналов здесь являются лог.«0», поэтому

RS-триггер на элементах И-НЕ имеет инверсные статические входы. Структурная

схема триггера и его УГО приведены на рисунках 4, в, г.[1; 211]

При разработке цифровых схем, в

которые входят RS-триггеры, необходимо учитывать наличие запрещённого состояния

входных сигналов для RS-триггеров на элементах ИЛИ-НЕ S=R=1, а для RS-триггеров

на элементах И-НЕ  Условие

нормального функционирования для обеих схем RS-триггеров можно записать в

следующем виде: SR ≠ 1

Условие

нормального функционирования для обеих схем RS-триггеров можно записать в

следующем виде: SR ≠ 1

Если в разрабатываемой

схеме такое сочетание входных сигналов в принципе возможно, то эту ситуацию

необходимо исключить путём включения во входную цепь <#"806398.files/image029.jpg">

Рисунок 10. Синхронные RS-триггеры:

Синхронные RS-триггеры имеют три

входа: S, R и C. Применение синхронизации не устраняет неопределённое состояние

триггера, возникающее при одновременной подаче единичных сигналов на все три

входа. Поэтому условием нормального функционирования является следующее

неравенство: SRC ≠ 1

Кроме трёх основных входов,

синхронные RS-триггеры снабжаются ещё входами асинхронной установки состояния

триггера- ŚиŔ. Они предназначены для

подачи приоритетных сигналов установки триггера в исходное состояние (0 или 1)

в начале цикла работы независимо от воздействия сигналов на входах S и R, то

есть в обход схемы управления.

По своему воздействию на состояние

триггера входы Ś и Ŕ являются самыми главными и поэтому на УГО отделяются от остальных

сигналов горизонтальной линией. [7; 260]

3. RS-триггеры S, R и E-типов

В отличие от обычных

RS-триггеров у триггеров S, R и E-типов комбинация

<#"806398.files/image030.gif">

Рисунок 11. RS-триггер

Е-типа

Схема работает как обычный

RS-триггер, но при подаче сигналов S=R=1 вентили D5 и D6 обеспечивают закрытое

состояние элементов D1 и D2, поэтому выходное состояние триггера Q остаётся без

изменения.

Если исключить из схемы Рисунка6

элемент D6, то при подаче на вход сигналов S=R=1 блокируется только элемент D2,

на выходе которого устанавливается «1», а на выходе D1 формируется «0». Эти

сигналы устанавливают триггер в состояние Q=1, или подтверждают его, если до

подачи сигналов S=R=1 триггер находился в состоянии Q=1. Такой триггер

называется RS-триггером S-типа.

Если исключить из схемы Рисунка 6

элемент D5, оставив элемент D6, то при подаче на вход сигналов S=R=1

блокируется только элемент D1, поэтому триггер устанавливается в состояние Q=0

или подтверждают его, если до подачи сигналов S=R=1 триггер находился в

состоянии Q=0. Такой триггер называется RS-триггером R-типа. [12]

Глава 2. Регистр, как устройство выполнения

функции приема, хранения и передачи информации

Основным классификационным признаком

регистров являются способ записи двоичного кода в регистр и его выдача, т.е.

различают параллельные, последовательные (сдвигающие) и

параллельно-последовательные регистры. Параллельный регистр выполняет операцию

записи параллельным кодом. Последовательный регистр осуществляет запись

последовательным кодом, начиная с младшего или старшего разряда, путем

последовательного сдвига кода тактирующими импульсами.

Параллельно-последовательные

регистры имеют входы как для параллельной, так и для последовательной записи кода

числа. Кроме того, сдвигающие регистры делятся на одно- и

двунаправленные(реверсивные). Однонаправленные регистры осуществляют сдвиг кода

влево или вправо, а двунаправленные - и влево, и вправо.

Основой построения регистров

являются синхронные RS-триггеры или, предпочтительнее, В-триггеры. Принцип

построения простейшего параллельного т-разрядного регистра показан на рисунке

12.

Рисунок 12. Параллельный регистр

В параллельном регистре цифры кода

подаются на D-вход соответствующих триггеров. Запись осуществляется при подаче

логической единицы на вход С. Код снимается с выходов Q. Параллельные регистры

служат только для хранения информации в виде параллельного двоичного кода и для

преобразования прямого кода в обратный и наоборот.

Последовательные регистры, помимо

хранения информации, способны преобразовывать последовательный код в

параллельный и наоборот. При построении последовательных регистров триггеры

соединяются последовательно путем подключения выхода Q i-го триггера ко входу D

i-го триггера, как это показано на рисунке 13. [15; 96]

Рисунок 13. Последовательный регистр

В последовательных регистрах

принципиально необходимо, чтобы новый сигнал на выходе Q i-го триггера возникал только после

окончания синхросигнала. Для выполнения этого условия в последовательных

регистрах необходимо применять двухступенчатые триггеры.

При действии каждого очередного

тактового импульса код, содержащийся в регистре, сдвигается на один разряд. Для

схемы, приведенной на рисунке 2, сдвиг кода происходит вправо (в сторону

младших разрядов). Действительно, сигнал выхода Q i+1-го триггера действует на

вход D i-го триггера, а сигнал выхода Q i-го триггера действует на вход D

i-1-го триггера. При действии синхросигнала i-й триггер примет состояние

i+1-го, а i-1-й - состояние i-го триггера, т.е., произойдет сдвиг кода вправо

на один разряд.

Параллельный двоичный код

одновременно снимается с выходов Q триггеров. Для сдвига кода влево необходимо,

чтобы сигнал с выхода Q i-1-го триггера подавался на вход Q i-го (старшего)

триггера.

Реверсивные регистры должны

содержать логические схемы управления, обеспечивающие прохождение сигнала с

выхода Q i-го триггера на вход D i-1-го триггера при сдвиге кода вправо и

прохождение этого же сигнала на вход D i+1-го при реализации сдвига кода влево.

Схема построения реверсивного регистра приведена на рисунке 14.

Рисунок 14. Реверсивный регистр

Направление сдвига кода определяется

подачей требуемых сигналов управления на соответствующие входы. Так, в схеме,

показанной на рис. 210, при подаче на вход S0 напряжения логической единицы

сдвиг кода будет происходить влево (в сторону старших разрядов), поскольку

логическая схема управления 2И - 2И - 2ИЛИ будет разрешать прохождение сигналов

с выходов Q i-го триггера на вход D i-го триггера, и наоборот, при подаче на

вход S1 напряжения логической единицы будет разрешено прохождение сигнала с

выхода Q i-го триггера на вход D i1-го триггера - будет реализовываться сдвиг

кода вправо (в сторону младших разрядов).

Условно-графическое обозначение

параллельного, сдвигового и реверсивного регистров приведено на рисунке 15. [2;

115]

Рисунок 15. УГО параллельного,

сдвигового и реверсивного регистров.

Выводы микросхем, показанных на

рисунке 4, следующие: D1-DN - входы D-триггеров соответствующих разрядов при

записи информации в параллельном коде; Q1-QN - прямые выходы Q-триггеров; С -

вход тактовых импульсов; R - вход обнуления; S0,S1 - входы управления

направлением сдвига; VR - вход последовательного кода при сдвиге вправо (R - от

англ. Right), при сдвиге кода влево применяется обозначение VL - (Left).

Основную массу регистров,

применяемых на практике, представляют регистры сдвига, т.к. помимо операции

хранения они могут осуществлять преобразование параллельного кода в

последовательный и наоборот, прямого кода - в обратный и наоборот, выполнять

арифметические и логические операции, временную задержку и деление частоты. [4;

100]

Заключение

триггер регистр

микросхема цифровой

Одним из ведущих

направлений развития современной микроэлектронной элементной базы являются БИС

(большие интегральные микросхемы) памяти, которые служат основой для построения

запоминающих устройств в аппаратуре различного назначения. Номенклатуру

микросхем памяти отечественного производства характеризует большое разнообразие

конструктивно-технологических и схемотехнических исполнений, функциональных

возможностей, электрических характеристик, областей применения.

Для хранения

небольших объёмов информации широко применяют регистры. Номенклатура микросхем

регистров хорошо развита и разнообразна. По принципу построения различают

регистры хранения и сдвига. Важнейшими характеристиками регистров являются разрядность и

быстродействие. Разрядность определяет число разрядов двоичной кодовой

комбинации, которая может быть записана в регистр. Быстродействие характеризует

максимальную частоту, с которой может производиться запись и чтение информации.

Регистры хранения служат для записи, хранения и считывания информации. Для

хранения информации могут использоваться RS- или D-триггеры, причем число

триггеров должно быть равно числу разрядов кодовой комбинации. Такие регистры

представляют собой совокупность последовательно соединенных триггеров, как

правило, двухступенчатых. Число триггеров, определяется разрядностью

записываемой кодовой комбинации. [4; 112]

По направлению

сдвига информации различают регистры со сдвигом вправо (т.е. в сторону младшего

разряда), со сдвигом влево (в сторону старшего разряда) и реверсивные,

допускающие сдвиг в обе стороны. [7; 279]

Литература

1.

Бабич Н.Л., Жуков И.А. Основы цифровой схемотехники: Учебное пособие. - С-П.,

2007. - 402с.

2.

Балашов Е.П., Григорян В.М. Микро- и мини ЭВМ., Л., -1984. - 376с.

3.

Бухгалтерский учет: Учеб. пособие. 3-е изд., перераб. и доп. /О.А. Левкович,

И.Н. Бурцева. - Мн.: Амалфея, 2005. - 800 с.

4.

Калабеков Б.А. Цифровые устройства и микропроцессорные системы. - М: Телеком,

2000. - 100-122с.

5.

Куракин В.Л. Свободные регистры сдвига. I. - В сб.: Труды по дискретной

математике. Т. 9. - М.: Гелиос-АРВ, 2006. - 232с.

6.

Ланских В.Г. Основы схемотехники. - К., 2002. - 78с.

7.

Морисита И. Аппаратные средства ЭВМ. Пер. с япон., - М.: Мир, 1988. - 279с.

8.

Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. - М.,

2001. - 379с.

.

Новиков Ю.В. Схемотехника. - М., 2002. - 384с.

10.

Потемкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат. -

1988. - с.87-96, 102-107.