Разработка топологии дешифратора

ИНСТИТУТ

НАНОТЕХНОЛОГИЙ, ЭЛЕКТРОНИКИ И ПРИБОРОСТРОЕНИЯ

(ИНЭП)

Кафедра

РТЭ

КУРСОВАЯ

РАБОТА

По

курсу: «Проектирование интегральных микросхем»

На

тему: «Разработка топологии дешифратора»

Выполнил:

студент гр. ЭПбо4-3

Медведко К. В.

Проверил:

Денисенко М. А.

Таганрог

2015

Введение

Основное понятие в этой курсовой работе -

интегральная схема. Интегральная схема (микросхема) - миниатюрное электронное

устройство, состоящее из большого количества радиоэлектронных элементов,

конструктивно и электрически связанных между собой. Обычно интегральная схема

создается для выполнения конкретной функции. По сути, микросхема объединяет в

себе какую-то электронную схему, где все элементы (транзисторы, диоды,

резисторы, конденсаторы) и электрические связи между ними конструктивно

выполнены на одном кристалле. Поскольку размеры отдельных компонентов очень

малы (микро- и нанометры), то на одном кристалле при современном развитии

технологий, можно поместить более миллиона электронных компонентов.

Интегральные схемы делятся на группы по

нескольким критериям. По степени интеграции - количеству элементов, размещенных

на кристалле. По типу обрабатываемого сигнала: цифровые, аналоговые и

аналого-цифровые. По технологии их производства и используемых материалов -

полупроводниковые, пленочные и т.д.

По способу изготовления различают

полупроводниковые и пленочные интегральные микросхемы. В полупроводниковых

интегральных микросхемах все ЭРЭ и часть межсоединений сформированы в

приповерхностном слое полупроводниковой (обычно кремниевой) подложки. В

пленочных интегральных микросхемах пассивные ЭРЭ изготовлены в виде

совокупности тонких (менее 1 мкм) или толстых (10-60 мкм) пленок, нанесенных на

диэлектрическую подложку.

Гибридные интегральные микросхемы (ГИС)

представляет собой комбинацию пленочных ЭРЭ с миниатюрными бескорпусными

дискретными приборами (полупроводниковыми интегральными микросхемами,

транзисторами, диодами), расположенных на общей диэлектрической подложке. ЭРЭ,

которые являются неотъемлемой составной частью интегральной микросхемы и не

могут быть выделены из нее как самостоятельное изделие, называют элементами

интегральной микросхемы, а дискретные активные ЭРЭ ГИС - навесными компонентами

(или просто компонентами) , подчеркивая тем самым, что их изготавливают отдельно

в виде самостоятельных приборов, которые могут быть приобретены изготовителем

ГИС как покупные изделия. В отличие от дискретных компонентов элементы

интегральной микросхемы называют интегральными.

Часто под интегральной схемой (ИС) понимают

собственно кристалл или плёнку с электронной схемой, а под микросхемой (МС,

чипом) - ИС, заключённую в корпус. В то же время выражение чип-компоненты

означает «компоненты для поверхностного монтажа» (в отличие от компонентов для

пайки в отверстия на плате).

Классификация ИС

Степени интеграции

В зависимости от степени интеграции применяются

следующие названия интегральных схем:

малая интегральная схема (МИС) - до 100

элементов в кристалле,

средняя интегральная схема (СИС) - до 1000

элементов в кристалле,

большая интегральная схема (БИС) - до 10 тыс.

элементов в кристалле,

сверхбольшая интегральная схема (СБИС) - более

10 тыс. элементов в кристалле.

Ранее использовались также теперь устаревшие

названия: ультрабольшая интегральная схема (УБИС) - от 1-10 млн до 1 млрд

элементов в кристалле и, иногда, гигабольшая интегральная схема (ГБИС) - более

1 млрд. элементов в кристалле. В настоящее время, в 2010-х, названия «УБИС» и

«ГБИС» практически не используются, и все микросхемы с числом элементов более

10 тыс. относят к классу СБИС.

Технология изготовления

Полупроводниковая микросхема - все элементы и

межэлементные соединения выполнены на одном полупроводниковом кристалле

(например, кремния, германия, арсенида галлия, оксида гафния).

Плёночная интегральная микросхема - все элементы

и межэлементные соединения выполнены в виде плёнок:

толстоплёночная интегральная схема;

тонкоплёночная интегральная схема.

Гибридная микросхема (часто называемая

микросборкой), содержит несколько бескорпусных диодов, бескорпусных

транзисторов и(или) других электронных активных компонентов. Также микросборка

может включать в себя бескорпусные интегральные микросхемы. Пассивные

компоненты микросборки (резисторы, конденсаторы, катушки индуктивности) обычно

изготавливаются методами тонкоплёночной или толстоплёночной технологий на

общей, обычно керамической подложке гибридной микросхемы. Вся подложка с

компонентами помещается в единый герметизированный корпус.

Смешанная микросхема - кроме полупроводникового

кристалла содержит тонкоплёночные (толстоплёночные) пассивные элементы,

размещённые на поверхности кристалла.

Вид обрабатываемого сигнала

Аналоговые.

Цифровые.

Аналого-цифровые.

Аналоговые микросхемы - входные и выходные

сигналы изменяются по закону непрерывной функции в диапазоне от положительного до

отрицательного напряжения питания.

Цифровые микросхемы - входные и выходные сигналы

могут иметь два значения: логический ноль или логическая единица, каждому из

которых соответствует определённый диапазон напряжения. Например, для микросхем

типа ТТЛ при напряжении питания +5 В диапазон напряжения 0…0,4 В соответствует

логическому нулю, а диапазон от 2,4 до 5 В - логической единице; для микросхем

ЭСЛ-логики при напряжении питания −5,2 В диапазон от −0,8 до −1,03

В - логической единице, а от −1,6 до −1,75 В - логическому нулю.

Аналого-цифровые микросхемы совмещают в себе

формы цифровой и аналоговой обработки сигналов, например, усилитель сигнала и

аналого-цифровой преобразователь.

Типы логики

Основным элементом аналоговых микросхем являются

транзисторы (биполярные или полевые). Разница в технологии изготовления

транзисторов существенно влияет на характеристики микросхем. Поэтому нередко в

описании микросхемы указывают технологию изготовления, чтобы подчеркнуть тем

самым общую характеристику свойств и возможностей микросхемы. В современных

технологиях объединяют технологии биполярных и полевых транзисторов, чтобы

добиться улучшения характеристик микросхем.

Микросхемы на униполярных (полевых) транзисторах

- самые экономичные (по потреблению тока):

МОП-логика (металл-оксид-полупроводник логика) -

микросхемы формируются из полевых транзисторов n-МОП или p-МОП типа;

КМОП-логика (комплементарная МОП-логика) -

каждый логический элемент микросхемы состоит из пары взаимодополняющих

(комплементарных) полевых транзисторов (n-МОП и p-МОП). Существует также

смешанная технология BiCMOS.

Микросхемы на биполярных транзисторах:

РТЛ - резисторно-транзисторная логика

(устаревшая, заменена на ТТЛ);

ДТЛ - диодно-транзисторная логика (устаревшая,

заменена на ТТЛ);

ТТЛ - транзисторно-транзисторная логика -

микросхемы сделаны из биполярных транзисторов с многоэмиттерными транзисторами

на входе;

ТТЛШ - транзисторно-транзисторная логика с

диодами Шоттки - усовершенствованная ТТЛ, в которой используются биполярные

транзисторы с эффектом Шоттки;

ЭСЛ - эмиттерно-связанная логика - на биполярных

транзисторах, режим работы которых подобран так, чтобы они не входили в режим

насыщения, - что существенно повышает быстродействие;

ИИЛ - интегрально-инжекционная логика.

КМОП и ТТЛ (ТТЛШ) технологии являются наиболее

распространёнными логиками микросхем. Где необходимо экономить потребление

тока, применяют КМОП-технологию, где важнее скорость и не требуется экономия

потребляемой мощности применяют ТТЛ-технологию. Слабым местом КМОП-микросхем

является уязвимость к статическому электричеству - достаточно коснуться рукой

вывода микросхемы и её целостность уже не гарантируется. С развитием технологий

ТТЛ и КМОП микросхемы по параметрам сближаются и, как следствие, например,

серия микросхем 1564 сделана по технологии КМОП, а функциональность и

размещение в корпусе как у ТТЛ технологии.

Дешифраторы

Электронное устройство для расшифровки

сообщений, передаваемых условными сигналами, и перевода информации на язык

воспринимающей системы.

Линейный или одноступенчатый дешифратор.

Дешифратор - это комбинационное устройство,

предназначенное для преобразования параллельного двоичного кода в унитарный,

т.е. позиционный код. Обычно указанный в схеме номер вывода дешифратора соответствует

десятичному эквиваленту двоичного кода, подаваемого на вход дешифратора в

качестве входных переменных, вернее сказать, что при подаче на вход устройства

параллельного двоичного кода на выходе дешифратора появится сигнал на том

выходе, номер которого соответствует десятичному эквиваленту двоичного кода.

Отсюда следует то, что в любой момент времени выходной сигнал будет иметь место

только на одном выходе дешифратора. Этот сигнал, в зависимости от типа

дешифратора, может иметь как уровень логической единицы (при этом на всех

остальных выходах - уровень логического 0), так и уровень логического 0 (при

этом на всех остальных выходах - уровень логической единицы).

Рассмотрим пример синтеза дешифратора 3 8,

следовательно, количество разрядов двоичного числа - 3, количество выходов - 8.

Таблица состояний дешифратора

|

Х3

|

Х2

|

Х1

|

Z0

|

Z1

|

Z2

|

Z3

|

Z4

|

Z5

|

Z6

|

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

|

0

|

1

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

Двухступенчатые дешифраторы на интегральных

микросхемах

Пример дешифратора для пятиразрядного двоичного

кода. Каждый дешифратор выполнен с управляющими входами, объединенными

конъюнктивно. При выполнении условия конъюнкции на выходе, номер которого

соответствует десятичному эквиваленту двоичного кода, появится уровень

логического «0». В противном случае все выходы находятся в состоянии логической

единицы (рис. 2.3). Как следует из рис. 2.3, пятиразрядный дешифратор, имеющий

32 выхода, выполнен на базе четырех дешифраторов с использованием лишь одного

дополнительного инвертора. Это достигнуто благодаря наличию входной управляющей

логики каждой интегральной микросхемы. Нетрудно заметить, что входная логика

дешифраторов КР1533ИД7 позволяет реализовать функцию дешифратора 23 без

дополнительных элементов, а функцию полного дешифратора 24 - с использованием

одного инвертора.

полупроводниковая микросхема

дешифратор

Логические функции двоичного дешифратора

Двоичный дешифратор работает по следующему

принципу. Пусть дешифратор имеет N входов. На входы подаётся двоичное слово  .

На выходах формируется код

.

На выходах формируется код  , разрядность

которого меньше или равна

, разрядность

которого меньше или равна  . Активным

становится разряд, номер которого равен численному представлению входного

слова. Под активностью разряда понимается принятие им значения логической

единицы, логического нуля или перевод в высокоимпедансное состояние -

отключение; конкретное значение зависит от используемой реализации дешифратора.

Остальные разряды остаются неактивными. Максимально возможная разрядность

выходного слова равна

. Активным

становится разряд, номер которого равен численному представлению входного

слова. Под активностью разряда понимается принятие им значения логической

единицы, логического нуля или перевод в высокоимпедансное состояние -

отключение; конкретное значение зависит от используемой реализации дешифратора.

Остальные разряды остаются неактивными. Максимально возможная разрядность

выходного слова равна  .

.

Дешифратор называется полным, если число выходов

равно максимально возможной разрядности выходного слова ( ).

Дешифратор называется неполным, если часть входных разрядов не используется (то

есть число выходов меньше

).

Дешифратор называется неполным, если часть входных разрядов не используется (то

есть число выходов меньше  ).

).

Функционирование одноединичного дешифратора,

активные выходные сигналы которого принимают значение логической единицы,

описывается системой конъюнкций:

…

Часто дешифраторы дополняются входом E (от англ.

enable) - «входом разрешения работы» (включения). Если на этот вход поступает

активный логический сигнал (единица или ноль), то один из выходов дешифратора

переходит в активное состояние, иначе все выходы неактивны вне зависимости от

состояния входов.

Функционирование одноединичного дешифратора с

дополнительным входом E описывается системой конъюнкций:

…

Обычно микросхемы дешифраторов выполняют с

инверсными выходами (то есть активный выбранный разряд принимает значение

логического нуля).

Двоичное слово на входе дешифратора часто

называют адресом.

Дешифратор, имеющий четыре информационных входа,

будет иметь, соответственно, восемь выходов. Дешифраторы, имеющие максимально

возможное количество выходов при данном количестве входов называются полными

дешифраторами. Промышленностью выпускаются дешифраторы, имеющие четыре входа и

десять выходов. Такие дешифраторы называются неполные дешифраторы. В неполном

дешифраторе существуют такие состояния входных сигналов, при которых не на

одном из выходов нет активного (лог. 0) сигнала. Такие дешифраторы применяются,

в том случае если используется так называемая двоично-десятичная система

исчисления. Что это такое. Это обычная двоичная система в которой используются

четыре двоичных разряда и эти разряды принимают только десять разных значений

от 00002 до 10012 (то есть от 010 до 910). Остальные комбинации двоичных

разрядов просто не используются. Такая система удобна для записи десятичных разрядов

в память компьютера, которая как мы уже знаем, работает с двоичными числами.

При этом в первые четыре бита ячейки памяти записывается первый разряд

десятичного числа. В следующие четыре бита - второй десятичный разряд и так

далее. Такие четверки байтов называются тетрадами. Такая форма представления

числа значительно упрощает операции с десятичными числами и вывод их, на какие

ни будь индикаторные устройства. Достаточно, например, к каждой группе из

четырех двоичных разрядов подключить описанный выше дешифратор, имеющий четыре

входа данных и десять выходов и к выходам этого дешифратора подключить

индикатор, имеющий для каждой цифры свой светящийся элемент, и мы всегда на

индикаторе будем видеть содержимое этих разрядов в удобном нам виде. Правда нам

придется немного видоизменить правила преобразования таких чисел (сложения,

вычитания и т. д.). Придется учитывать, что после числа 10012 (1010) в такой

системе идет число 00002 (010) и перенос в следующую тетраду.

Дешифраторов с более, чем тремя входами данных,

выполненных в виде отдельных микросхем, практически не производят, так как они

имели бы недопустимо большое количество выводов. Однако наличие входов выбора

микросхемы позволяет каскадировать дешифраторы. На рисунке приведена схема

дешифратора с пятью входами данных и тридцатью двумя выходами. Дешифратор

собран по схеме каскадирования. Для построения такой схемы потребовался один

дешифратор на два входа и четыре дешифратора на три входа.

Дешифраторы широко применяются в

микропроцессорной технике. И главное их применение - это обеспечение

возможности подключения нескольких регистров или ячеек памяти к одной шине

данных.

Схема дешифратора с пятью входами данных и

тридцатью двумя выходами

Примеры микросхем дешифраторов

Микросхема ИДЗ имеет четыре адресных входа 1,

2,4, 8, два инверсных входа стробирования S, объединенных по И, и 16 ╦выходов

0-15 Если на обоих входах стробирования лог. 0, на том из выходов, номер

которого соответствует десятичному эквиваленту входного кода (вход 1 - младший

разряд, вход 8 -старший), будет лог. 0, на остальных выходах - лог. 1. Если

хотя бы на одном из входов стробирования S лог. 1, то независимо от состояний

входов на всех выходах микросхемы формируется лог. 1.

Наличие двух входов стробирования существенно

расширяет возможности использования микросхем. Из двух микросхем ИДЗ,

дополненных одним инвертором, можно собрать дешифратор на 32 выхода.

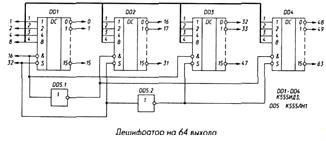

Дешифратор на 64 выхода собирается из четырех

микросхем ИДЗ и двух инверторов

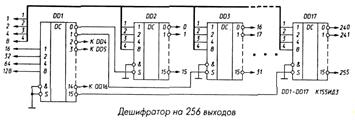

Дешифратор на 256 выходов - из 17 микросхем ИДЗ

Микросхема ИД4 содержит два дешифратора на

четыре выхода каждый с объединенными адресными входами и разделенными входами

стробирования Лог 0 на выходах первого (верхнего по схеме) дешифратора

формируется (аналогично ИДЗ) лишь при наличии на обоих стробирующих входах лог

0.Соответствующее условие для второго дешифратора - наличие на одном из его

входов стробирования лог 1(вывод 1), а на другом - лог 0 (вывод 2). Такая

структура микросхемы позволяет использовать ее в различных вариантах включения.

Наличие трех входов стробирования позволяет

простыми средствами объединять микросхемы для наращивания разрядности

дешифратора. Три микросхемы ИД7 можно объединить в дешифратор на 24 выхода без

дополнительных элементов (соединение микросхем DD1 -DD3), четыре микросхемы и

инвертор - в дешифратор на 32 выхода. Дополнив схему еще четырьмя микросхемами

ИД7 и инвертором, можно получить дешифратор на 64 выхода.

Микросхема К555ИД6 - неполный дешифратор

двоично-десятичного кода 1-2-4-8. Как и микросхема К155ИД1, она имеет четыре

адресных входа 1,2,4,8, но ее десять выходов 0-9 выполнены по стандартной

схеме. При подаче на входы 1, 2 4,8 кода чисел 0-9 на том выходе, номер которого

соответствует десятичному эквиваленту входного кода, появляется лог. 0, на

остальных выходах -лог. 1: при входных кодах, соответствующих числам 10-15, на

всех выходах - лог. 1.

Техническое задание

Разработать топологию дешифратора в соответствии

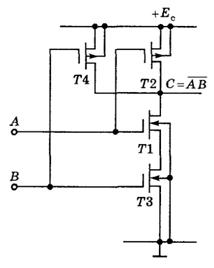

со схемой, приведенной на рис. КП.3.

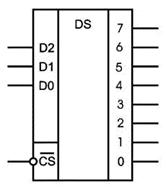

Рис. КП.3. Схема дешифратора в соответствии с

вариантом курсового проекта

Параметры:

минимальный топологический размер - 90 нм;

отношение ширины к длине канала транзисторов с

электронной

проводимостью - 3;

отношение ширины к длине канала транзисторов с

дырочной

максимально допустимая площадь топологии - 30000

мкм2;

максимально допустимое количество слоев

металлизации - 3.

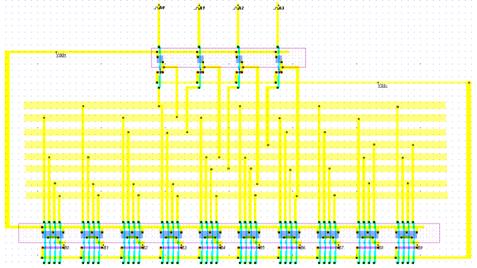

Разработка топологии дешифратора в программе

MicroWind 3.1

Разработка топологии фрагментов интегральной

схемы

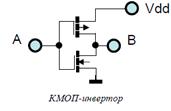

КМОП-инвертор

Топология инвертора

КМОП «И-НЕ»

Топология элемента И-НЕ

Топология дешифратора в соответствии с вариантом

курсового проекта

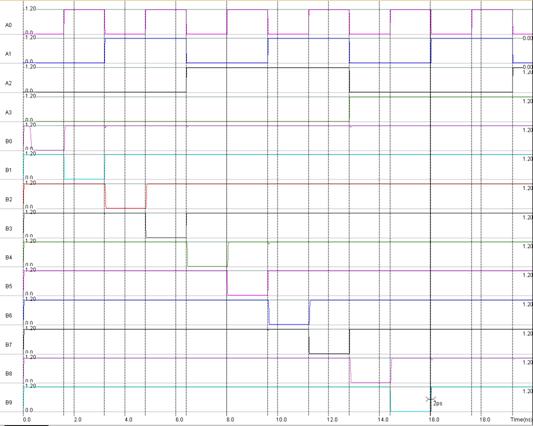

Результат моделирования

Проверка выполнения правил проектирования

По диаграммам видно, что устройство работает без

ошибок и помех. Соблюдены почти все технические нормы задания. Проверка

выполнена поэтапно в процессе разработки топологии с помощью Design Rule Checker.

Заключение

В данной работе была разработана топология

дешифратора в соответствии с вариантом курсового проекта и рассчитаны параметры

интегральной логической схемы. Приведенные рисунки подтверждают полное

соответствие разработанной ИМС требованиям технического задания. Топология

микросхемы разработана с учетом технологических возможностей оборудования.

Линейные размеры элементов и расстояния между ними больше минимально

допустимых, что обеспечит меньшую погрешность при производстве, а следовательно,

и больший выход годных изделий при групповом производстве.

Электронные параметры схемы учитывают работу

схемы в реальных условиях, а именно скачки питающего напряжения. Разработанная

ИМС полностью пригодна для эксплуатации в современной электронной аппаратуре.