Разработка интегрального цифрового устройства

Федеральное

агентство по связи и информатике

Государственное

образовательное учреждение высшего профессионального образования

Сибирский

государственный университет телекоммуникаций и информатики

Курсовая

работа

Разработка

интегрального цифрового устройства

Выполнил:

Симон А.С.

студент гр.

В-67

Проверил:

Савиных В.Л.

г.

Новосибирск - 2008 г.

Содержание

1.

Разработка электрической схемы цифрового устройства

.1

Задание к первой части

.2

Упрощение и преобразование

.3

Выбор типа логики и конкретных серий

.4

Электрическая схема цифрового устройства

.5

Проверка условий

Вывод

.

Электрический расчет цифровой схемы

.1

Задание ко второй части

.2

Электрический расчет схемы

.3

Таблицы

.4

Расчет мощностей

.5

Таблица истинности

Вывод

.

Разработка топологии в гибридном варианте

.1

Пленочные проводники

.2

Навесные элементы

.3

Топологический чертеж ИМС

Вывод

Заключение

Список

используемой литературы

1. Разработка электрической схемы

цифрового устройства.

.1 Задание к первой части

Даны четыре уравнения:

Дополнительные требования:

· Выходной ток Iвых≤30мА

· Общая потребляемая мощность

устройства Pпотр≤100мВт

· Время задержки распространения

сигнала tзд.р.ср≤70нсек

1.2 Упрощение

и преобразование

Y2 оставим без

изменения

1.3 Выбор типа логики и конкретных

серий

При реализации данного цифрового

устройства будем использовать 6 ЦИМС с логикой КМДП (DD1, DD2, DD3, DD4, DD5 и DD7) 1 ЦИМС с

логикой ТТЛ (DD6), чтобы

была необходимая мощность. Чтобы обеспечить большой выходной ток, будем

использовать параллельное включение Eпит=5В.

|

|

|

|

Iпотр.ср

|

I0вых

|

I1вых

|

tзд.р.ср

|

|

DD1

|

1564ЛИ1

|

4

лог. эл.

|

2И

|

5мкА

|

5,2мА

|

-0,5мА

|

19,5нс

|

|

DD2

|

1564ЛЛ1

|

4

лог. эл.

|

2ИЛИ

|

5мкА

|

5,2мА

|

-0,5мА

|

17нс

|

|

DD3

|

1564ЛЕ1

|

2 лог. эл.

|

2ИЛИ-НЕ

|

4мкА

|

5,2мА

|

-0,5мА

|

17нс

|

|

DD4

|

КР1554ЛЛ1

|

4

лог. эл.

|

2ИЛИ

|

4мкА

|

24мА

|

-24мА

|

7,25нс

|

|

DD5

|

КР1554ЛП5

|

4

лог. эл.

|

ИСКЛ.

ИЛИ

|

8мкА

|

24мА

|

-24мА

|

13,5нс

|

|

DD6

|

КР1531ЛИ1

|

1 лог. эл.

|

2И

|

10,65мА

|

60мА

|

1мА

|

6,3нс

|

|

DD7

|

КР1554ЛЛ1

|

3 лог. эл.

|

2ИЛИ

|

4мкА

|

24мА

|

-24мА

|

7,25нс

|

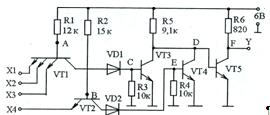

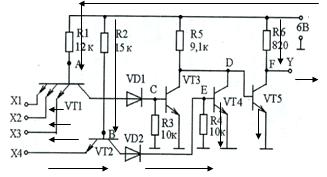

1.4 Электрическая схема цифрового

устройства

1.5 Проверка условий

Время задержки распространения

Для Y1

tзд.р.ср=t1+t4+t5=19.5+7.25+13.5=40.25нс<70нс

Для Y2

tзд.р.ср=

t1++t3+t4=19.5+17+7.25=43.75нс<70нс

Для Y3

tзд.р.ср=

t2+t5+t7=17+13.5+7.25=37.75нс<70нс

Для Y4

tзд.р.ср=

t1+t5+t6=19.5+13.5+6.3=39.3нс<70нс

Потребляемая мощность.

Pпотр = Eпит

* ∑Iпотр = 5*(4*5*10-3+4*5*10-3+2*4*10-3+4*4*10-

+4*8*10-3 + 1*10,65 + 3*4*10-3)

= 53,79мВт < 100мВт

Выходной ток

Для Y1

Iвых=2*24мА=48мА>30мА

Для Y2

Iвых=2*24мА=48мА>30мА

Для Y3

Iвых=2*24мА=48мА>30мА

Для Y4

Iвых=60мА>30мА

Вывод

Получили электрическую схему цифрового

устройства, которая реализует данные 4 уравнения и соответствует дополнительным

условиям

2.Электрический расчет цифровой

схемы

2.1 Задание ко второй части

Рассчитать данную схему

2.2 Электрический расчет схемы

а) х1=0 х2=0 х3=0 х4=0

UА=U0вх

+Uэб=0,1+0,7=0,8В

UВ=U0вх

+Uэб=0,1+0,7=0,8В

,8В не хватит, чтобы открыть три p-n

перехода.

VD1, VD2,

VT3, VT4

- закрыты.

UC=UE=0

IКVT1

=

IКVT2=IR3=IR4

=

IБVT3=IБVT4=0

IR1 = (Eп-

UА)/R1

= (6-0,8)/12=0,433мА0вх1

= I0вх2=I0вх3=

IR1/3=0,144мАR2

= (Eп-

UВ)/R2

= (6-0,8)/15 = 0,347мА0вх4

= IR2=0,347мАD

= Uэб=0,7ВБVT5

= IR5 = (Eп-

UD)/R5 = (6-0,7) / 9,1 = 0,582мА0вых= I0вх=0,433мА

(берем самый худший случай)

Предположим. Что VT5

находится в режиме насыщения.

IБVT5>IБ.НАС → VT5

действительно находится в режиме

насыщение

IR6 = (Eп- UКЭ.НАС)/R6=(6-0,1)/0,82=7,2мА

UF= UКЭ.НАС =0.1В

IКVT5= I0вых+ IR6=0.433+7.2=7.633мА

Y=0

б) х1=1 х2=1 х3=1 х4=1

UА=

0,6+0,7+0,7=2В

UB=0,6+0,7+0,7=2В

VT1 и VT2 - в

инверсном режиме.

IR1=(Eп-

UА)/R1=(6-2)/12=0,333мА1вх1=I1вх2=I1вх3=

IR1ВИ=0,333*0,05=0,0166мАКVT1=

IR1+ I1вх1+

I1вх2+

I1вх3=0,383мА

UC

=

Uэб = 0,7В

IR3

=

UC/R3

= 0,7/10 = 0,07мА

IБVT3

=

IКVT1-

IR3 =

0,383-0,07 = 0,313мА

IR2

=

(Eп- UВ)/R2

= (6-2)/15 = 0,266мА

I1вх4

= IR2ВИ

= 0,266*0,05 = 0,0133мАКVT2

= IR2+ I1вх4

= 0,28мАЕ

= Uэб

= 0,7ВR4

= UЕ/R4

= 0,7/10 = 0,07мАБVT4

=

IКVT2-

IR4 =

0,28-0,07 = 0,21мА

Предположим, что VT3

и VT4 находятся в

режиме насыщения.

IБVT3>IБ.НАС.VT3, IБVT4>IБ.НАС.VT4 → VT3 и VT4

действительно находятся в режиме насыщения.

UD= UКЭ.НАС =0.1В →

VT5 - закрыт.

IБVT5=0, IКVT5=0

IR5= (Eп- UD)/R5=(6-0,1)/9,1=0,648мА

I1вых = I1вх=0,0166мА

(берем самый худший случай)

IR6= I1вых

=0,0166мА

UF=Eп- IR6*R6=6-0,0166*0,82=5.986В

Y=1

в) х1=0 х2=0 х3=0 х4=1 (аналогично

а) и б)

UА=U0вх +Uэб=0,1+0,7=0,8В

,8В не хватит, чтобы открыть три p-n перехода.

VD1, VT3 - закрыты.

UC=0

IКVT1=IR3= IБVT3=0

IR1=(Eп-

UА)/R1=(6-0,8)/12=0,433мА0вх1=I0вх2=I0вх3=

IR1/3=0,144мАB=0,6+0,7+0,7=2В

цифровой интегральный

микросхема топология

VT2 - в

инверсном режиме.

IR2=(Eп- UВ)/R2=(6-2)/15=0,266мА

I1вх4=

IR2ВИ=0,266*0,05=0,0133мАКVT2=

IR2+ I1вх4=0,28мАЕ=Uэб=0,7ВR4=

UЕ/R4=0,7/10=0,07мАБVT4= IКVT2- IR4=0,28-0,07=0,21мА

Предположим, что VT4

находится в режиме насыщения.

IБVT4>IБ.НАС.VT4 → VT4

действительно находятся в режиме насыщения.

UD= UКЭ.НАС =0.1В →

VT5 - закрыт.

IБVT5=0, IКVT5=0

IR5= (Eп- UD)/R5=(6-0,1)/9,1=0,648мА

IR6= I1вых

=0,0166мА

UF=Eп- IR6*R6=6-0,0166*0,82=5.986В

Y=1

2.3 Таблицы

|

UA

|

UB

|

UC

|

UD

|

UE

|

UF

|

VT1

|

VT2

|

VT3

|

VT4

|

VT5

|

VD1

|

VD2

|

|

0000

|

0,8

|

0,8

|

0

|

0,7

|

0

|

0,7

|

эб-откр.

кб-закр.

|

эб-откр.

кб-закр.

|

закр

|

закр

|

нас.

|

закр

|

закр

|

|

1111

|

2

|

2

|

0,7

|

0,1

|

0,7

|

5,986

|

инвер.

|

инвер.

|

нас.

|

нас.

|

закр

|

откр

|

откр

|

|

0001

|

0,8

|

2

|

0

|

0,1

|

0,7

|

5,986

|

эб-откр.

кб-закр.

|

инвер.

|

закр

|

нас.

|

закр

|

закр

|

откр

|

|

IВХ1

|

IВХ2

|

IВХ3

|

IВХ4

|

IR1

|

IR2

|

IR3

|

IR4

|

IR5

|

IR6

|

IБVT3

|

IБVT4

|

IБVT5

|

|

0000

|

0,144

|

0,144

|

0,144

|

0,347

|

0,433

|

0,347

|

0

|

0

|

0,582

|

7,2

|

0

|

0

|

0,582

|

|

1111

|

0,016

|

0,016

|

0,016

|

0,013

|

0,333

|

0,266

|

0,07

|

0,07

|

0,648

|

0,016

|

0,313

|

0,21

|

0

|

|

0001

|

0,144

|

0,144

|

0,144

|

0,013

|

0,433

|

0,266

|

0

|

0,07

|

0,648

|

0,016

|

0

|

0,21

|

0

|

.4 Расчет мощностей

|

Входная

комбинация

|

Токи,

мА

|

Потребляемая

мощность, мВт

|

|

Вх.1

|

Вх.2

|

Вх.3

|

Вх.4

|

IR1

|

IR2

|

IR5

|

IR6

|

|

|

0

|

0

|

0

|

0

|

0,433

|

0,347

|

0,582

|

7,2

|

51,37

|

|

1

|

1

|

1

|

1

|

0,333

|

0,266

|

0,648

|

0,016

|

7,58

|

|

0

|

0

|

0

|

0

|

0,433

|

0,266

|

0,016

|

8,18

|

P=Eп*(

IR1+ IR2+ IR5+ IR6)

Для первой комбинации P=6*(0,433+0,347+0,582+7,2)=51,37мВт

Для второй комбинации P=6*(0,333+0,266+0,648+0,016)=7,58мВт

Для третьей комбинации P=6*(0,433+0,266+0,648+0,016)=8,18мВт

Максимальные мощности резисторов

|

Максимальный

ток, мА

|

Мощность

резисторов, мВт

|

|

IR1

|

IR2

|

IR3

|

IR4

|

IR5

|

IR6

|

PR1

|

PR2

|

PR3

|

PR4

|

PR5

|

PR6

|

|

0.433

|

0.347

|

0,07

|

0,07

|

0.648

|

7.2

|

2,25

|

1,8

|

0,049

|

0,049

|

3,82

|

42,45

|

PRi=Ii2*RiR1=(0.433)2*12=2.25мВтR2=(0.347)2*15=1,8мВт

PR3=(0.07)2*10=0,049мВт

PR4=(0.07)2*10=0,049мВт

PR5=(0,648)2*9,1=3,82мВт

PR6=(7,2)2*0,82=42,45мВт

2.5 Таблица истинности

Если х4 равен 0 и х1 или х2, х3 равен 0, то VT3

и VT4 будут закрыты, а VT5

будет открыт → Y=0,

в остальных случаях Y=1…

|

х1

|

х2

|

х3

|

х4

|

Y

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

0

|

1

|

1

|

|

0

|

0

|

1

|

0

|

0

|

|

0

|

0

|

1

|

1

|

1

|

|

0

|

1

|

0

|

0

|

0

|

|

0

|

1

|

0

|

1

|

1

|

|

0

|

1

|

1

|

0

|

0

|

|

0

|

1

|

1

|

1

|

1

|

|

1

|

0

|

0

|

0

|

0

|

|

1

|

0

|

0

|

1

|

1

|

|

1

|

0

|

1

|

0

|

0

|

|

1

|

0

|

1

|

1

|

1

|

|

1

|

1

|

0

|

0

|

0

|

|

1

|

1

|

0

|

1

|

1

|

|

1

|

1

|

1

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Данная схема реализует функцию Y=x1*x2*x3+x4…

Вывод

Рассчитали электрическую схему, определили

таблицу истинности и по ней определили какую функцию реализует заданная схема

3. Разработка топологии в гибридном

варианте

.1 Пленочные проводники

|

R1

|

R2

|

R3

|

R4

|

R5

|

R6

|

|

12

кОм

|

15

кОм

|

10

кОм

|

10

кОм

|

9,1

кОм

|

820

Ом

|

|

P,

мВт

|

2,25

|

1,8

|

0,049

|

0,049

|

3,82

|

42,45

|

|

КФ

|

12

|

15

|

10

|

10

|

9,1

|

0,82

|

|

lрасчетн.

|

1,16

|

1,16

|

0,16

|

0,16

|

1,32

|

1,32

|

|

bрасчетн.

|

0,0966

|

0,0773

|

0,016

|

0,016

|

0,145

|

1,61

|

|

l

|

2,4

|

3

|

2

|

2

|

1,8

|

1,6

|

|

b

|

0,2

|

0,2

|

0,2

|

0,2

|

0,2

|

1,3

|

Возьмем сплав PC-3001

RS=1000

Ом/кв. P0=20мВт/мм2

Найдем КФ = RI/

RS

КФ1 = R1/

RS=12

КФ2 = R2/

RS=15

КФ3 = R3/

RS=10

КФ4 = R4/

RS=10

КФ5 = R5/

RS=9,1

КФ6 = R6/

RS=0,82

Найдем

Найдем bI=lI/KФI

b1=l1/KФ1=1,16/12=0,0966

b2=l2/KФ2=1,16/15=0,07733=l3/KФ3=0,16/10=0,0164=l4/KФ4=0,16/10=0,0165=l5/KФ5=1,32/9,1=0,145

b6=l6/KФ6=1,32/0,82=1,61

Так как у пленочных резисторов есть

ограничения, то l и b примут

следующие значения, приведенные в таблице

3.2 Навесные элементы

Выбираем активные элементы - диоды и

транзисторы, руководствуясь следующими принципами:

· Диоды и транзисторы должны быть бескорпусными;

· Должны быть предназначены для работы

в импульсном режиме;

· Структура транзистора n-p-n;

· Коэффициент передачи тока БТ  >50;

>50;

· Для диодов:

,

,  ;

;

· Для транзисторов:

,

,  ,

,

1. В

качестве диодов VD1,

VD2 возьмем КД904А

Uобр.max=10В

Iпр.max=5мА,

габариты 1×1×1

. В качестве транзисторов VT2,

VT3, VT4,

VT5 используем КТ331А

Iк.max

= 20мА

Uкэmax

= 10В

Pкmax

= 15мВт

габариты 1×1×0,8

. В качестве транзистора VT1

берем многоэмитерный транзистор

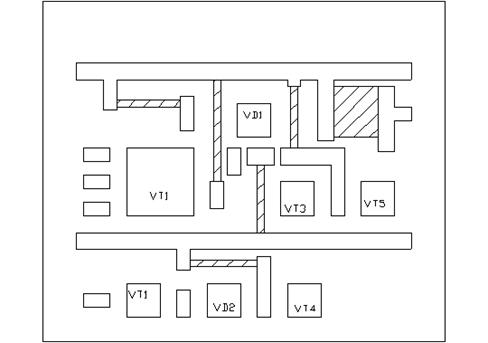

3.3 Топологический чертеж ИМС

Площадь, занимаемая резисторами:

SR=SR1+SR2+SR3+SR4+SR5+SR6=2.4*0.2+3*0.2+2*0.2+2*0.2+1.8*0.2+1.6*1.

3=4.32мм2

Площадь, занимаемая навесными элементами схемы:

S=SVD1+SVD2+SVT1+SVT2+SVT3+SVT4+SVT5+SVT6=1+1+4+1+1+1+1+1=11мм2

Площадь подложки должна быть не менее

5*(4,32+11)=76,6мм2

В качестве подложки выбираем ситалл размерами 12×10…

Масштаб 10:1

Вывод

В третье части я разработал топологический

чертеж в гибридном варианте, учитывая основные ограничения, накладываемые

тонкопленочной технологией.

Заключение

В данной курсовой работе мы составили электрическую

схему на основе базовых цифровых интегральных микросхем (ЦИМС), для этой

электрической схемы и учитывая дополнительные требования к этой схеме мы

выбрали для 6 ЦИМС логику КМДП и для 1 ЦИМС логику ТТЛ; произвели электрический

расчет цифрового устройства и построил топологию этого устройства.

В результате проделанной работы мы освоили

основные положения Т.Э. и их практическое применение, а именно:

Закрепили основные положения алгебры логики, при

помощи чего, можно минимизировать функции и реализовывать их в различных

логических базисах и на практических элементах;

Освоили принципы выбора логики ИМС и расчета их

параметров; -Научились рассчитывать простейшие цифровые интегральные

микросхемы;

Так же освоили принцип подбора материалов и

активных элементов для микросхемы, и последующей разработки топологии этой

схемы.

Список используемой литературы

1.

Электронные, квантовые приборы и микроэлектроника: Учеб. пособие для вузов /

Ю.Л. Бобровский, С.А. Корнилов, И.А. Кратиров и др.; Под ред. проф. Н.Д. Федорова.-

М.: Радио и связь, 1998. - 580 с.

.

Ефимов, Козырь. Основы микроэлектроники.- М.: Сов. Радио,1980г.

.

В.Л. Савиных. Микроэлектроника. 1999

.

А.Н. Удальцов. Разработка интегрального цифрового устройства. 2008