Розроблення та синтез VHDL-моделей елементів пристроїв захисту інформації

МІНІСТЕРСТВО

ОСВІТИ І НАУКИ, МОЛОДІ ТА СПОРТУ УКРАЇНИ

НАЦІОНАЛЬНИЙ

УНІВЕРСИТЕТ «ЛЬВІВСЬКА ПОЛІТЕХНІКА»

КУРСОВА

РОБОТА

з

навчальної дисципліни: “ Комп`ютерні методи високорівневого проектування

пристроїв захисту ” на тема:

“Розроблення

та синтез VHDL-моделей елементів пристроїв захисту інформації”

Львів

- 2012

Зміст

Завдання

Аналітичний

розділ з роз’ясненням та аналізом основних принципів побудови та реалізації

пристрою в ПЛІС

Розділ

з описом заданих алгоритмів шифрування та режимів обробки даних

Розділ

з описом розробки архітектури пристрою та його структурної схеми на рівні між

регістрових передач

Розділ

з описом розробки VHDL - моделей компонент пристрою та VHDL - пристрою в цілому

Розділ

з описом розробки системи тестування для виконання тестування пристрою та з

результатами симуляції пристрою у формі часових діаграм, результати синтезу

пристроюинтез розробленої VHDL - моделі пристрою в ПЛІС

Висновки

Список

використаної літератури

тестування пристрій

захист інформація

Завдання

Відповідно до НЗК (номера залікової

книжки) визначити варіант завдання наступним чином: (аb тоd 25 + 1), аb - дві

останні цифри НЗК. Варіант завдання подано в таблиці нижче.

Виконати архітектурне проектування

та розробити VHDL - модель пристрою реалізації заданих завданням режимів

обробки даних. Як модуль шифрування використати імітаційну модель пристрою, що

виконує заданий завданням алгоритм симетричного блокового шифрування.

Розробити систему тестування та з її

допомогою виконати функціональну симуляцію розробленої VHDL - моделі пристрою.

Для магістрів - виконати синтез

розробленої VHDL - моделі пристрою в ПЛІС за власним вибором, а також виконати

часову симуляцію розробленої VHDL - моделі пристрою з допомогою розробленої

системи тестування.

|

Варіант

|

Алгоритм СБШ

|

Режими обробки даних

|

|

1

|

AES-128

|

CTR, СВС, ECB

|

Аналітичний розділ з роз’ясненням та

аналізом основних принципів побудови та реалізації пристрою в ПЛІС

Етапи проектування програмних

моделей процесорів на рівні міжрегістрових передач та їх реалізації у

програмовних логічних інтегральних схемах (ПЛІС) зображено на рис. 1.

Рис. 1. Етапи проектування

програмних моделей процесорів на рівні міжрегістрових передач та їх реалізації

у програмовних логічних інтегральних схемах.

Структура процесора визначається під

час його функціональної декомпозиції: кожен з модулів процесора повинен бути

функціонально незалежним. В загальному критеріями якості розбиття схеми на

модулі є функціональна незалежність модулів та кількість міжмодульних з'єднань

(чим менше - тим краще).

Розробник, володіючи методикою

проектування програмних моделей процесорів мовами опису апаратних засобів,

створює якісну програмну модель. Під час розробки програмної моделі та після її

закінчення проводиться функціональна симуляція, яка дає змогу виявити помилки,

відлагодити роботу процесора та підтвердити його відповідність технічному

завданню.

Для ефективного тестування окремих

компонент та всієї програмної моделі процесора розробляють системи тестування. Система

тестування - це спеціальне середовище (модель), у яке поміщається тестований

пристрій і яке імітує роботу реальної системи, у якій буде працювати надвелика

інтегральна схема. Архітектура системи тестування розробляється відповідно до

вимог конкретного тестованого пристрою. Помилки, що виявляються на етапі

функціональної симуляції, усуваються шляхом модифікації програмної моделі

процесора на етапі його опису мовою опису апаратних засобів. Такі помилки

усуваються найлегше, проте інколи це вимагає змін в архітектурі процесора.

Після функціональної симуляції

проводиться логічний синтез програмної моделі процесора у ПЛІС. На цьому етапі

код з мови опису апаратних засобів транслюється у код, який використовується як

вхідний при програмуванні кристалу. На етапі логічного синтезу процесора у ПЛІС

отримуються його характеристики - частота роботи та розмір на кристалі (затрати

обладнання). Таким чином розробник може визначити, чи задовольняє розробка

вимоги технічного завдання, чи ні. Дуже важливим є те, що засоби логічного

синтезу ПЛІС генерують результуючий файл мовою опису апаратних засобів, який

відображає фізичну модель синтезованого процесора. Ця модель є описом процесора

на рівні логічних комірок (примітивів) ПЛІС, яку використовують, і відображає

всі часові затримки при проходженні інформації у кристалі. Розробник,

використовуючи розроблену систему тестування, може перевірити, чи є

працездатною фізична модель процесора. Цей процес називається часовою

симуляцією синтезованого процесора. Помилки, що виникають на етапі часової

симуляції, виявляються та усуваються значно важче ніж ті, що виникають на етапі

функціональної симуляції. Такі помилки свідчать або про неякісно розроблену

програмну модель процесора, або про невдале використання особливостей примітивів

ПЛІС (наприклад, наявність так званих хибних шляхів, завищення частоти

синхроімпульсів тощо). Якщо синтезована модель успішно витримала часову

симуляцію, то наступним кроком є програмування ПЛІС. Результат перевірки

пристрою, реалізованого у ПЛІС, дає змогу зробити висновок про відповідність

розробленого процесора технічному завданню. Якщо процесор відповідає технічному

завданню, то його передають на етап системного тестування. Якщо системний тест

не виявив помилок, то процесор готовий до використання. Помилки, які можуть

виникнути на цьому етапі, виявити та усунути найважче. Вони можуть бути

спричинені відсутністю сигналу скиду у певних елементах ПМП чи порушенням

синхронізації. Інколи це трапляється через порушення температурного режиму

роботи кристалу, завищення частоти синхроімпульсів чи від відхилення взірця

кристалу від його стандартних технічних параметрів.

Типовий склад конструкторської

документації проекту програмної моделі процесора є наступним:

функціональна модель процесора,

написана мовою опису апаратних засобів, VHDL або Verilog (VHDL - модель,

Verilog - модель);

фізичні моделі процесора,

орієнтовані на його реалізацію в конкретних кристалах ПЛІС;

модель системи тестування для

перевірки функцій та параметрів процесора;

текстова документація з детальним

описом інтерфейсу та принципів функціонування процесора, яка складається з його

функціонального опису, інструкції користувача та рекламного листа.

Розділ з описом заданих алгоритмів

шифрування та режимів обробки даних

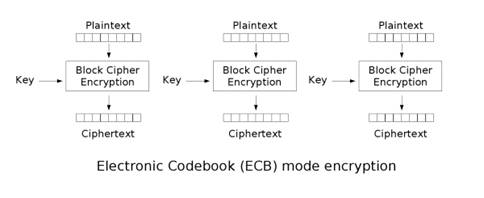

Електронна книга кодів (ECB)

Найпростішим з режимів шифрування є

режим електронної книги кодів (англ. electronic codebook, ECB). Повідомлення

розбивається на блоки і кожен блок шифрується окремо.

Рис.2 Схеми шифрування і

розшифрування режиму електронної кодової книги.

Вадою цього методу є те, що однакові

блоки відкритого тексту шифруються в однакові блоки шифротексту; отже шаблон

погано приховується. Цей режим не забезпечує серйозну безпеку повідомленням, і

його взагалі не радять використовувати в криптографічних протоколах.

Типовий приклад ступеня збереження

шаблонів ECB відкритого тексту в шифротексті можна побачити, коли ECB

використовують для шифрування bitmap зображень, які використовують великі площі

однорідних кольорів. Хоча колір кожного окремого пікселя зашифровано, загальну

картинку можна розрізнити як маску однокольорових пікселів картинки на вході.

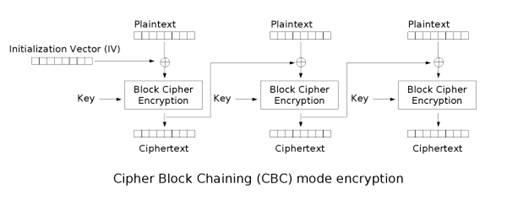

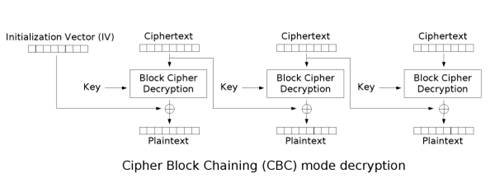

Ланцюгування шифроблоків

(CBC)винайшла режим ланцюгування шифроблоків (англ. cipher-block chaining, CBC)

у 1976. В CBC режимі, кожен блок відкритого тексту XOR-ять з попереднім

шифроблоком перед шифруванням. Так, кожен шифроблок, залежить від усіх блоків

оброблених до нього. Для отримання унікальних повідомлень потрібно

використовувати ініціалізаційний вектор у першому блоці.

Рис.3 Схеми шифрування і

розшифрування режиму ланцюгування шифроблоків.

Якщо перший блок має індекс 1,

математична формула для CBC шифрування буде наступною:

тоді як математична формула для CBC

розшифрування є такою:

найчастіше використовний режим.

Основна його вада це властива послідовність (тобто не можливість упаралелення),

і необхідність доповнення повідомлення до розміру кратного розміру блоку. Один

зі способів уникнути доповнення полягає в використанні методу викрадення

шифротексту. Зауважте, що зміна одного біта в відкритому тексті або IV впливає

на всі наступні шифроблоки.

Розшифрування з неправильним IV

спричиняє пошкодження першого блоку відкритого тексту, але наступні блоки

будуть правильними. Це відбувається через можливість відновити відкритий текст

з двох суміжних блоків шифротексту. Як наслідок, розшифрування можна упаралелити.

Зауважте, що зміна одного біту в шифротексті спричиняє повне пошкодження

відповідного блоку відкритого тексту, але інші блоки залишаються незачепленими.

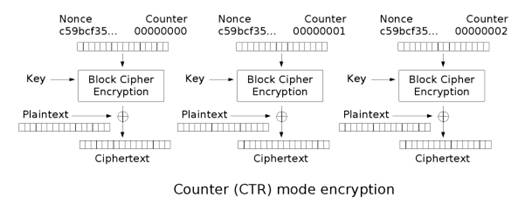

Лічильник (CTR)

Подібно до OFB, режим лічильника

перетворює блочний шифр в потоковий шифр. Він породжує наступний блок потоку

ключа шифруванням послідовних значень «лічильника». Лічильник може бути

будь-якою функцією, що видає послідовність, яка гарантовано не повторюється

впродовж тривалого часу, насправді найпростішими і найпоширенішими є прості

лічильники, що на кожному кроці збільшуються на одиницю. використання простої

детерміністичної функції викликає суперечки; критики кажуть, що «навмисне

використання відомого систематичного входу в криптосистемі становить

непотрібний ризик.» Наразі, режим CTR широко прийнятий, і проблеми похідні від

входової функції розпізнаються як слабкість використовного блочного шифру, а не

режиму CTR. Проте, існують пристосовані атаки подібні до атаки помилки

устаткування (англ. Hardware Fault Attack), які покладаються на використання

простого функції лічильника.

Режим CTR має подібні до OFB

характеристики, але також має можливість довільного доступу під час

розшифрування. Режим CTR добре підходить для використання на багатопроцесорній

машині, де блоки можна шифрувати паралельно. Більше того, він не потерпає від

проблеми короткого циклу, яка може вплинути на OFB.

Зауважте, що nonce на зображенні це

те саме, що й ініціалізаційний вектор на інших зображеннях. IV/nonce і

лічильник можна сполучати із використанням будь-якої операції без втрат

(конкатенації, додавання або XOR) для отримання унікального блоку лічильника

для шифрування.

Рис.4 Схеми шифрування і

розшифрування режиму лічильника.

У випадку використання режиму CTR з

одним nonce для шифрування цілого диску, повторне використання відтинку потоку

ключа уможливлює нескладну атаку. Отже, кожного разу за зміни навіть малої

ділянки даних, необхідно буде перешифрувати весь диск із використанням іншого

nonce для підтримки безпеки, що не практично.

Розділ з описом розробки архітектури

пристрою та його структурної схеми на рівні між регістрових передач

Розглянемо процес розробки VHDL -

моделі пристрою, який реалізує три режими блочного шифрування(ECB, CBC, CTR).

Структура пристрою складається з таких елементів: регістри для зберігання

вхідних даних, демультиплексорів, мультиплексорів, елементів логічного

додавання за модулем два. У складі інтерфейс них ліній є входи синхронізації,

входи та виходи даних. В пристрої присутні команди, які задають шифрування чи

розшифрування даних(ed) і режим блочного шифрування(em).

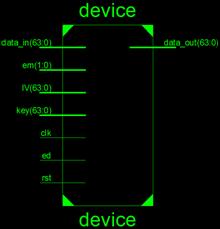

Опис інтерфейсу розробленого

пристрою є наступним:device is(: in std_logic;: in std_logic;: in std_logic;:

in std_logic_vector(1 downto 0);_in : in std_logic_vector(63 downto 0);: in

std_logic_vector(63 downto 0);: in std_logic_vector(63 downto 0);_out : out

std_logic_vector(63 downto 0)

);device;

Рис. 5 Структурна схема на рівні між

регістрових передач.

Спочатку вхідні дані(data_in, key,

IV) зберігаються у відповідних регістрах, дальше дані подаються на входи

відповідних елементів(мультиплексорів, демультиплексорів, елементів логічного

додавання за модулем два).

Розділ з описом розробки VHDL -

моделей компонент пристрою та VHDL - пристрою в цілому

Згідно із структурною схемою

пристрою описуємо елементи які представлені на схемі на мові опису апаратних

засобів VHDL. Загальни опис пристрою представлений у файлі device.vhd.

В описі архітектури об’являються 13

підсхем. Після ключового слова begin приводяться екземпляри опису. Кожний

екземпляр має карту портів(port map) Карта портів відображає зв'язок між

входами, виходами опису компонент і екземплярами компонент.

.vhd:IEEE;IEEE.STD_LOGIC_1164.all;device is(: in std_logic;: in std_logic;: in

std_logic;: in std_logic_vector(1 downto 0);_in : in std_logic_vector(63 downto

0);: in std_logic_vector(63 downto 0);: in std_logic_vector(63 downto 0);_out :

out std_logic_vector(63 downto 0)

);device;device of device is

RS_1_out : std_logic_vector(63 downto 0);RS_2_out : std_logic_vector(63 downto

0); RS_3_out : std_logic_vector(63 downto 0);RS_4_out : std_logic_vector(63

downto 0);MUX_1_out : std_logic_vector(63 downto 0);MUX_2_out :

std_logic_vector(63 downto 0);XOR_1_out : std_logic_vector(63 downto 0);AES_out

: std_logic_vector(63 downto 0);MUX_3_out : std_logic_vector(63 downto

0);XOR_2_out : std_logic_vector(63 downto 0);counter_out : std_logic_vector(63

downto 0);RS_5_out : std_logic_vector(63 downto 0);DMUX_OUT_1 :

std_logic_vector(63 downto 0);DMUX_OUT_2 : std_logic_vector(63 downto 0);RS_1(

: in std_logic;: in std_logic;_in_RS1 : in std_logic_vector(63 downto 0);_out_RS1

: out std_logic_vector(63 downto 0)

);component;DMUX(_in : in std_logic_vector(63

downto 0);_dec : in std_logic;_mode : in std_logic_vector(1 downto 0);_1 : out

std_logic_vector(63 downto 0);_2 : out std_logic_vector(63 downto 0)

);component;RS_2( : in std_logic;: in

std_logic;_in_RS2 : in std_logic_vector(63 downto 0);_out_RS2 : out

std_logic_vector(63 downto 0)

);component;RS_3( : in std_logic;: in

std_logic;_in_RS3 : in std_logic_vector(63 downto 0);_out_RS3 : out

std_logic_vector(63 downto 0)

);component;RS_4( : in std_logic;: in

std_logic;_in_RS4 : in std_logic_vector(63 downto 0);_out_RS4 : out

std_logic_vector(63 downto 0)

);component;MUX_1(_in : in std_logic_vector(63

downto 0);_in : in std_logic_vector(63 downto 0);_dec : in std_logic;_mode : in

std_logic_vector(1 downto 0);_out : out std_logic_vector(63 downto 0)

);component;MUX_2(: in std_logic_vector(63

downto 0);_dec : in std_logic;_mode : in std_logic_vector(1 downto 0);_out :

out std_logic_vector(63 downto 0)

);component;XOR_1(_in : in std_logic_vector(63

downto 0);_in : in std_logic_vector(63 downto 0);_in : in std_logic_vector(63

downto 0); _out : out std_logic_vector(63 downto 0)

);component;AES(_in : in std_logic_vector(63

downto 0);_in : in std_logic_vector(63 downto 0);_out: out std_logic_vector(63

downto 0)

);component; counter(: in std_logic;: in

std_logic;_out : out std_logic_vector(63 downto 0)

);component;MUX_3(_in : in std_logic_vector(63

downto 0);_dec : in std_logic;_mode : in std_logic_vector(1 downto 0);_out :

out std_logic_vector(63 downto 0)

);component;XOR_2( _mode : in std_logic_vector(1

downto 0);_in : in std_logic_vector(63 downto 0);_in : in std_logic_vector(63

downto 0);_in : in std_logic_vector(63 downto 0);_out : out std_logic_vector(63

downto 0)

);component; RS_5( : in std_logic;: in

std_logic;_in_RS5 : in std_logic_vector(63 downto 0);_out_RS5 : out

std_logic_vector(63 downto 0)

);component;

R1: RS_1

port map(clk,rst,data_in,RS_1_out);

D: DMUX

port map(data_in,ed,em,DMUX_OUT_1,DMUX_OUT_2);

R2: RS_2

port map(clk,rst,IV,RS_2_out);

R3: RS_3

port map(clk,rst,key,RS_3_out);

M1: MUX_1

port map(IV,RS_4_out,ed,em,MUX_1_out);

C: counter

port map(clk,rst,counter_out);

M2: MUX_2

port map(counter_out,ed,em,MUX_2_out);

X1: XOR_1

port map(DMUX_OUT_1,MUX_1_out,MUX_2_out,

XOR_1_out);

A: AES

port map(XOR_1_out,key,AES_out);

R4: RS_4

port map(clk,rst,AES_out,RS_4_out);

M3: MUX_3

port map(IV,ed,em,MUX_3_out);

X2: XOR_2

port

map(em,AES_out,DMUX_OUT_2,MUX_3_out,XOR_2_out);

R5: RS_5

port map(clk,rst,XOR_2_out,RS_5_out);

data_out <=

RS_5_out;device;_1.vhd:IEEE;IEEE.STD_LOGIC_1164.all;RS_1 is ( : in std_logic;:

in std_logic;_in_RS1 : in std_logic_vector(63 downto 0);_out_RS1 : out

std_logic_vector(63 downto 0)

);RS_1;RS_1 of RS_1 is(c, r)(r = '1') then

data_out_RS1 <= (others => '0'); (c'event and c = '1') then _out_RS1

<= data_in_RS1;Null;if;process;RS_1;_2.vhd:IEEE;IEEE.STD_LOGIC_1164.all;RS_2

is ( : in std_logic;: in std_logic;_in_RS2 : in std_logic_vector(63 downto

0);_out_RS2 : out std_logic_vector(63 downto 0)

);RS_2;RS_2 of RS_2 is(c, r)(r = '1') then

IV_out_RS2 <= (others => '0'); (c'event and c = '1') then _out_RS2 <=

IV_in_RS2;Null;if;process;RS_2;_3.vhd:IEEE;IEEE.STD_LOGIC_1164.all;RS_3 is ( :

in std_logic;: in std_logic;_in_RS3 : in std_logic_vector(63 downto 0);_out_RS3

: out std_logic_vector(63 downto 0)

);RS_3;RS_3 of RS_3 is(c, r)(r = '1') then

key_out_RS3 <= (others => '0'); (c'event and c = '1') then _out_RS3 <=

key_in_RS3;Null;if;process;RS_3;_4.vhd:IEEE;IEEE.STD_LOGIC_1164.all;RS_4 is ( :

in std_logic;: in std_logic;_in_RS4 : in std_logic_vector(63 downto 0);_out_RS4

: out std_logic_vector(63 downto 0)

);RS_4;RS_4 of RS_4 is(c, r)(r = '1') then

data_out_RS4 <= (others => '0'); (c'event and c = '1') then _out_RS4

<= data_in_RS4;Null;if;process;RS_4;_5.vhd:IEEE;IEEE.STD_LOGIC_1164.all;RS_5

is ( : in std_logic;: in std_logic;_in_RS5 : in std_logic_vector(63 downto

0);_out_RS5 : out std_logic_vector(63 downto 0)

);RS_5;RS_5 of RS_5 is(c, r)(r = '1') then

data_out_RS5 <= (others => '0'); (c'event and c = '1') then _out_RS5

<=

data_in_RS5;Null;if;process;RS_5;_1.vhd:IEEE;IEEE.STD_LOGIC_1164.all;MUX_1

is(_in : in std_logic_vector(63 downto 0);_in : in std_logic_vector(63 downto

0);_dec : in std_logic;_mode : in std_logic_vector(1 downto 0);_out : out std_logic_vector(63

downto 0)

);MUX_1;MUX_1 of MUX_1 is: process(IV_in,

RG4_in, enc_dec, enc_mode)(enc_dec='1') thenenc_mode is"00" =>

MUX1_out <= (others => '0'); "01" => MUX1_out <=

IV_in;"10" => MUX1_out <= IV_in;others => MUX1_out <=

(others => '0'); case;if;(enc_dec='0') thenenc_mode is"00" =>

MUX1_out <= (others => '0'); "01" => MUX1_out <= (others

=> '0'); "10" => MUX1_out <= IV_in;others => MUX1_out

<= (others => '0'); case;if;process;MUX_1;_2.vhd:IEEE;IEEE.STD_LOGIC_1164.all;MUX_2

is(: in std_logic_vector(63 downto 0);_dec : in std_logic;_mode : in

std_logic_vector(1 downto 0);_out : out std_logic_vector(63 downto 0)

);MUX_2;

-}} End of automatically maintained sectionMUX_2

of MUX_2 is: process(counter, enc_dec, enc_mode)(enc_dec='1') thenenc_mode is"00"

=> MUX2_out <= (others => '0'); "01" => MUX2_out <=

(others => '0'); "10" => MUX2_out <= counter;others =>

MUX2_out <= (others => '0'); case;if;(enc_dec='0') thenenc_mode

is"00" => MUX2_out <= (others => '0'); "01" =>

MUX2_out <= (others => '0'); "10" => MUX2_out <=

counter;others => MUX2_out <= (others => '0');

case;if;process;MUX_2;_1.vhd:IEEE;IEEE.STD_LOGIC_1164.all;XOR_1 is( _in : in

std_logic_vector(63 downto 0);_in : in std_logic_vector(63 downto 0);_in : in

std_logic_vector(63 downto 0); _out : out std_logic_vector(63 downto 0)

);XOR_1;XOR_1 of XOR_1 is : process(d_in, M1_in,

M2_in)_out <= d_in xor M1_in xor

M2_in;process;XOR_1;.vhd:IEEE;IEEE.STD_LOGIC_1164.all;AES is(_in : in

std_logic_vector(63 downto 0);_in : in std_logic_vector(63 downto 0);_out: out

std_logic_vector(63 downto 0);_dv : out std_logic

);AES;AES of AES is: process(X_in, K_in)_out

<= X_in xor K_in;process;AES;_3.vhd:IEEE;IEEE.STD_LOGIC_1164.all;MUX_3

is(_in : in std_logic_vector(63 downto 0);_dec : in std_logic;_mode : in

std_logic_vector(1 downto 0);_out : out std_logic_vector(63 downto 0)

);MUX_3;MUX_3 of MUX_3 is: process(I_in,

enc_dec, enc_mode)(enc_dec='1') thenenc_mode is"00" => MUX3_out

<= (others => '0'); "01" => MUX3_out <= (others =>

'0'); "10" => MUX3_out <= (others => '0'); others =>

MUX3_out <= (others => '0'); case;if;(enc_dec='0') thenenc_mode

is"00" => MUX3_out <= (others => '0'); "01" =>

MUX3_out <= I_in;"10" => MUX3_out <= (others => '0');

others => MUX3_out <= (others => '0');

case;if;process;MUX_3;_2.vhd:IEEE;IEEE.STD_LOGIC_1164.all;XOR_2 is(_mode : in

std_logic_vector(1 downto 0);_in : in std_logic_vector(63 downto 0);_in : in

std_logic_vector(63 downto 0);_in : in std_logic_vector(63 downto 0);_out : out

std_logic_vector(63 downto 0)

);XOR_2;XOR_2 of XOR_2 is: process(A_in, d_in,

M3_in)

d_out <= A_in xor d_in xor M3_in;

end

process;XOR_2;_vhd:IEEE;IEEE.std_logic_1164.all;IEEE.std_logic_unsigned.all;IEEE.std_logic_arith.all;counter

is (: in std_logic;: in std_logic;_out : out std_logic_vector(63 downto 0)

);counter;counter of counter iscnt :

std_logic_vector(63 downto 0);: process(c, r, cnt)(r = '1') then cnt <=

(others => '0'); (c'event and c = '1') then<= cnt+'1';cnt <=

cnt;if;process;_out <= cnt;counter;.vhd:IEEE;IEEE.STD_LOGIC_1164.all;DMUX is(_in

: in std_logic_vector(63 downto 0);_dec : in std_logic;_mode : in

std_logic_vector(1 downto 0);_1 : out std_logic_vector(63 downto 0);_2 : out

std_logic_vector(63 downto 0)

);DMUX;DMUX of DMUX is: process(d_in, enc_dec,

enc_mode)(enc_dec='1') thenenc_mode is"00" => out_1 <= d_in;

out_2 <= (others => '0');"01" => out_1 <= d_in; out_2

<= (others => '0');"10" => out_1 <= (others => '0');

out_2 <= d_in; others => out_1 <= (others => '0'); out_2 <=

(others => '0'); case;if;(enc_dec='0') thenenc_mode is"00" =>

out_1 <= d_in; out_2 <= (others => '0'); "01" => out_1

<= d_in; out_2 <= (others => '0'); "10" => out_1 <=

(others => '0'); out_2 <= d_in;others => out_1 <= (others =>

'0'); out_2 <= (others => '0'); case;if;process;DMUX;

Розділ з описом розробки системи тестування тестування

для виконання тестування пристрою та з результатами симуляції пристрою у формі

часових діаграм, результати синтезу пристрою

Тестування програмних моделей пристроїв, один з

найважливіших етапів розробки. На даному етапі виявляється левина частка помилок

при проектуванні.

Відтестованою вважається та програмна модель,

яка успішно пройшла функціональну і часову симуляцію. Для проведення тестування

використовують спеціально розроблені системи тестування програмних моделей,

побудовані як моделі реальних середовищ, у яких працюватимуть ці пристрої.

Структура системи тестування в цілому залежить від специфіки конкретного

тестованого пристрою, оскільки вона повинна, з одного боку, якомога повніше

відображати реальне середовище роботи пристрою, а з іншого - забезпечувати

можливість перевірки коректності його роботи у всіх можливих ситуаціях. Як

правило, для програмних моделей спеціалізованих пристроїв, що реалізують певні

стандартизовані алгоритми, використовують стандартизовані тестові набори.

Зазначимо, що тестування кожної окремої моделі потребує застосування спеціально

розробленої системи тестування з використанням специфічних тестових наборів.

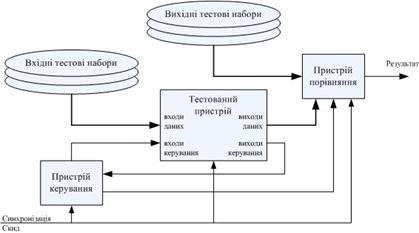

Структуру типової системи тестування програмних

моделей представлено на рис.1 .

Рис. 6. Структура типової системи тестування

програмних моделей процесорів.

На вхід тестованого пристрою подають вхідні

тестові набори, результати обробки яких порівнюють з зразковими значеннями -

вихідними тестовими наборами. Порівняння результатів обробки вхідних тестових

наборів і зразкових значень виконує пристрій порівняння. Результат його роботи

визначає коректність (чи некоректність) функціонування тестованого пристрою.

Функції керування тестованим пристроєм та пристроєм порівняння виконує пристрій

керування системою тестування. Сигнали синхронізації та початкового скиду

системи зазвичай подають ззовні.

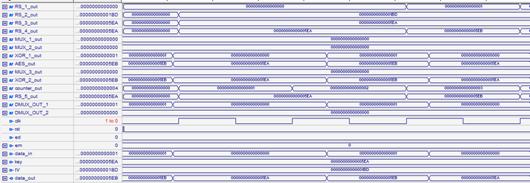

Рис. 7 Результат симуляції

розшифрування даних в режимі CTR.

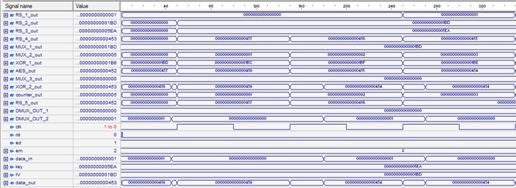

Рис. 8 Результат симуляції

розшифрування даних в режимі CBC.

Рис. 9 Результат симуляції

розшифрування даних в режимі CTR.

интез розробленої VHDL - моделі

пристрою в ПЛІС

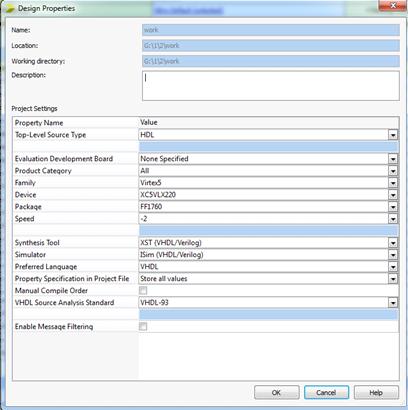

Для синтезу розробленої VHDL -

моделі пристрою в ПЛІС використовуємо програму Xilinx ise. Спочатку необхідно

створити проект і вибрати параметри проекту. Параметри проекту які використані

у даній курсовій роботі представлені на рис.10:

Рис.10 Параметри проекту.

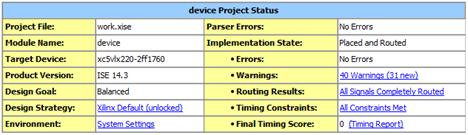

Наступним кроком є перевірка коду на

синтаксичні помилки. Це здійснюється за допомогою команди Check Syntax. Після

успішної перевірки синтаксису здійснюємо побудову ПЛІС за допомогою команди

Implement Top Module. Після побудови ми отримаємо схему ПЛІС(рис. 11,12).

Рис. 11 схема ПЛІС.

Рис. 12 схема ПЛІС.

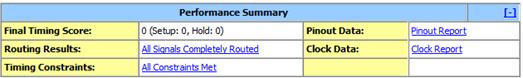

Також ми отримаємо характеристики

програмованої логічної інтегральної схеми(рис. 13,14,15)

Рис. 13 характеристики ПЛІС.

Рис. 14 характеристики ПЛІС.

Рис. 13 характеристики ПЛІС.

Висновки

Під час виконання даної курсової

роботи я узагальнив знання, отримані під час вивчення навчальної дисципліни

" Комп`ютерні методи високорівневого проектування пристроїв захисту",

та трансформував ці знання в практичні навички для побудови пристрою, який

здійснює три режими блочного шифрування(ECB, CBC, CTR). В пристрої присутні

команди, які задають шифрування чи розшифрування даних(ed) і режим блочного

шифрування(em). Для побудованого пристрою була розроблені програма тестування.

В даній роботі за допомогою програми

Xilinx ise розроблений пристрій був реалізований на програмованій логічній

інтегральній схемі. До отриманої ПЛІС були представлені характеристики і

структурна схема.

Список використаної літератури

Коркішко

Т.А., Мельник А.О., Мельник В.А. Алгоритми та процесори симетричного блокового

шифрування. / Львів, БАК, 2003. - 182 с.46, "Data Encryption Standard",

Federal Information Processing Standard (FTPS), Publication 46, National Bureau

of Standards, U.S. Department of Commerce, Washington D.C.81, "Operational

modes of DES", Federal Information Processing Standard (FIPS), Publication

81, National Bureau of Standards, U.S. Department of Commerce, Washington D.C.

ГОСТ28147-89.

Система обработки информации. Защита криптографическая. Алгоритм

криптографического преобразования. М. Госстандарт СССРJ., Rijmen V. AES

Proposal: Rijndael // First Advanced Encryption Standard (AES) Conference. -

Ventura, CA, 1998.+ Verilog = синтез за минуты: Учебное пособие/ В.И. Хаханов,

И.В. Хаханова.-Харьков: ХНУРЭ.- 2006.- 264 с.

В.А.

Мельник, В.Б. Дудикевич. "Тестування генераторів ядер комп'ютерних

пристроїв" // Вісник Національного університету "Львівська

політехніка" "Автоматика, вимірювання та керування". - 2003.

№475. - с. 123-128.

Угрюмов

Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2000. - 528 с.

Суворова

Е.А., Шейнин Ю.Е. Язык VHDL для проектирования систем на СБИС: Учебное пособие.

/ ГУАП, СПб., 2001 - 212 с.

Мясников

В А., Игнатьев М.Б., Кочкин А.А., Шейнин Ю.Е. Микропроцессоры: системы

программирования и отладки. М: Энергоатомиздат, 1985. - 272 с.

Майоров

С.А., Новиков Г.И., Алиев Т.И. Основы теории вичислительных систем. - М.:

Высш.шк., 1978.-408 с.

ГОСТ

Р 50754-95. Язык описания аппаратуры цифровых систем VHDL. Описание языка.