Розробка комп'ютерних схем різного призначення: шифратори, дешифратори, мультиплексори, лічильники та регістри. Загальні характеристики електронних цифрових схем по булевих виразах. Розрахунок лічильника та регістрів. Значення логічних сигналів.

Розробка

комбінаційних та послідовних схем

1. Аналіз предметної області та постановка задачі

1.1 Загальні характеристики електроних цифрових схем ПЕОМ

Логічні елементи - пристрої, призначені

для обробки інформації в цифровій формі (послідовності сигналів високого - «1»

і низького - «0» рівнів в двійковій логіці, послідовність «0», «1» і «2» в

трійкової логіки, послідовності «0», «1», «2», «3», «4», «5», «6», «7», «8» і

«9» в десятковій логіці). Фізично логічні елементи можуть бути виконані механічними,

електромеханічними (на електромагнітних реле), електронними (на діодах і

транзисторах), пневматичними, гідравлічними, оптичними та інші.

З розвитком електротехніки від механічних логічних елементів

перейшли до електромеханічним логічним елементам (на електромагнітних реле), а

потім до електронних логічних елементів на електронних лампах, пізніше - на

транзисторах. Після доказу в 1946 р. теореми Джона фон Неймана про економічності

показових позиційних систем числення стало відомо про переваги двійковой і трійковой систем числення в

порівнянні з десятковою системою числення. Від десяткових логічних елементів

перейшли до двійкових логічних елементів. Двоичность і троичность дозволяє значно скоротити

кількість операцій і елементів, що виконують цю обробку, порівняно з

десятковими логічними елементами.

Все можливо

логічних функцій і відповідних їм логічних елементів, де x -

логічних функцій і відповідних їм логічних елементів, де x -

основа системи числення, n - число входів (аргументів), m - число виходів, тобто нескінченне число логічних

елементів.

основа системи числення, n - число входів (аргументів), m - число виходів, тобто нескінченне число логічних

елементів.

Всього можливі 2(2)*1 =24 =16

двійкових двухвходовых логічних елементів і 2

двійкових трехвходових логічних елементів (Булева функція). Крім

16 двійкових двухвходових логічних елементів і 256 трьохвходових бінарних

логічних елементів можливі 19 683 двухвходових трійкових логічних елементів і 7

625 597 484 987 трьохвходових трійкових логічних елементів.

двійкових трехвходових логічних елементів (Булева функція). Крім

16 двійкових двухвходових логічних елементів і 256 трьохвходових бінарних

логічних елементів можливі 19 683 двухвходових трійкових логічних елементів і 7

625 597 484 987 трьохвходових трійкових логічних елементів.

Тригер

(тригерна система) - клас електронних пристроїв, що володіють здатністю

тривалий час перебувати в одному з двох стійких станів і чергувати їх під

впливом зовнішніх сигналів. Кожен стан трігера легко розпізнаються за

значенням вихідної напруги. За характером дії трігери відносяться до імпульсних пристроїв - їх активні елементи

(транзистори, лампи) працюють у ключовому режимі, а зміна станів триває дуже

короткий час.

Відмінною особливістю тригера як функціонального пристрою є

властивість запам'ятовування двійкової інформації. Під пам'яттю тригера мають на увазі

здатність залишатися в одному з двох станів і після припинення дії перемикає

сигнал. Прийнявши одне з станів за «1», а інше за «0», можна вважати, що трігер зберігає (пам'ятає) один розряд числа, записаного в

двійковому коді.

При виготовленні тригерів застосовуються переважно

напівпровідникові прилади (зазвичай біполярні та польові транзістори), в минулому -

електромагнітні реле, електронні лампи. В даний час логічні схеми, у тому числі

з використанням трігерів, створюють в інтегрованих середовищах розробки під різні

програмовані логічні інтегральні схеми. Використовуються, в основному, в

обчислювальній техніці для організації компонентів обчислювальних систем:

регістрів, лічильників, процесорів, оперативної пам'яті.

Динамічний тригер являє собою керований

генератор, один з станів якого (одиничне) характеризується наявністю на виході

безперервної послідовності імпульсів певної частоти, а інше (нульове) -

відсутністю вихідних імпульсів.

До статичних тріггеров відносять пристрої, кожн стан яких

характеризується незмінними рівнями вихідної напруги (вихідними потенціалами):

високим - близькою до напруги живлення і низьким - близько нуля. Статичні

трігери за способом подання вихідної інформації часто називають потенційними.

Статичні (потенційні) трігери, в свою чергу, поділяються на

дві нерівні по практичному значенню групи - симетричні і несиметричні тригери.

Обидва класу реалізуються на двухкаскадном двухінверторном підсилювачі з

позитивним зворотним зв'язком.

Симетричні тригери відрізняє симетрія схеми і за структурою,

і за параметрами елементів обох плечей. Для несиметричних тригерів характерна

неідентичність параметрів елементів окремих каскадів, а також і зв'язків між

ними.

Асинхронний тригер змінює свій стан безпосередньо в момент

появи відповідного інформаційного сигналу(ів), з деякою затримкою дорівнює сумі

затримок на елементах, що складають даний тригер.

Синхронні тригери реагують на інформаційні сигнали тільки при

наявності відповідного сигналу на так званому вході синхронізації З (від англ.

clock). Цей вхід також позначають терміном «такт». Такі інформаційні сигнали

називають синхронними. Синхронні тригери у свою чергу підрозділяють на трігери

із статичним та з динамічним керуванням по входу синхронізації.

Комбінаційні схеми - це схеми, у яких

вихідні сигнали Y = (у1, у2,…, ум) у будь-який момент дискретного часу однозначно

визначаються сукупністю вхідних сигналів Х = (х1, х2,…, хп), що надходять у той

же момент часу t. Реалізується в КС спосіб обробки інформації називається

комбінаційним тому, що результат обробки залежить тільки від комбінації вхідних

сигналів і формується відразу при надходженні вхідних сигналів. Тому одним з достоїнств

комбінаційних схем є їх висока швидкодія. Перетворення інформації однозначно

описується логічними функціями виду Y=f(Х).

Логічні функції і відповідні їм комбінаційні

схеми поділяють на регулярні і нерегулярні структури. Регулярні структури

припускають побудову схеми таким чином, що кожен з її виходів будується за аналогією з попередніми. У

нерегулярних структурах така аналогія відсутня.

У практиці проектування ЕОМ накопичений величезний досвід по

синтезу різних схем. Багато регулярні структури покладені в основу побудови

окремих ІС малої і середньої ступені інтеграції чи окремих функціональних

частин ВІС і НВІС. З регулярних комбінаційних схем найбільш поширені

дешифратори, шифратори, схеми порівняння, комбінаційні суматори, комутатори та

ін.

Розглянемо принципи побудови подібних регулярних структур.

Дешифратори (ДШ) - це комбінаційні схеми з п входами і m =2n виходами.

Одиничний сигнал, що формується на одному з т виходів, однозначно відповідає

комбінації вхідних сигналів. Наприклад, розробка структури ДШ для п=3 згідно з

методикою, дозволяє отримати таблицю істинності і логічні залежності.

Шифратор (кодер) призначений для перетворення напруги

високого рівня на одному з m входів в паралельний двійковий код, що формується

на n виходах. Кількість входів і виходів пов'язані між собою співвідношенням

m=2n. Можливі варіанти шифраторів, в яких кодований вхідний сигнал низького

рівня, як, наприклад, у шифраторів К155ИВ1, К555ИВ1. Сигнал низького рівня,

який кодується, поступає на один з входів X0…X7. На інших входах повинні бути

сигнали високого рівня. На виходах Y0…Y2 формується двійковий код, який

відповідає тому входові, на якому знаходиться напруга низького рівня. Таким

чином, 8-ми різним позиціям напруги низького рівня на входах відповідає 8

різних комбінацій напруг на виходах.

Мікросхема має керуючий вхід (вхід стробу) V. Сигнали на цьому вході

дають дозвіл (V=0), або

забороняють (V=1) роботу ІМС в

режимі кодування. У випадку заборони на всіх виходах встановлюються напруги високого

рівня незалежно від сигналів на входах.

Основну свою функцію деякі шифратори реалізують з пріоритетом

кодованого сигналу. Наприклад, в шифраторі К155ИВ1 функція пріоритету

виконується наступним чином: якщо на його входах з'явиться декілька сигналів низького

рівня, то код на виході буде відповідати сигналові низького рівня, що

знаходиться на вході зі старшим номером (при комбінаціях вхідних сигналів

11110111, 00000111, 10100111 результат буде один: на виході в усіх випадках

буде зформовано код 011, оскільки пріоритетом володіє нульовий сигнал на вході

X4). Мікросхеми шифраторів різних серій та їх параметри.

Дешифратор (декодер) виконує операцію перетворення

m-елементного паралельного коду на входах в сигнал високого (або низького)

рівня на одному з його n виходів. Дешифратор називається повним, якщо кількість

виходів рівна кількості можливих наборів вхідних сигналів, тобто n=2m. Неповний

дешифратор має меншу кількість виходів, як, наприклад, дешифратор К155ИД1, який

при чотирьох входах має тільки десять виходів. Мікросхеми дешифраторів різних

серій відрізняються швидкодією, енергоспоживанням, кількістю виходів (повні та

неповні), наявністю або відсутністю стробуючого входу. Наприклад, ІМС здвоєного

дворозрядного дешифратора низького рівня К155ИД4, К555ИД4 має по два стробуючі

входи в кожному дешифраторі, а однойменні інформаційні входи A та B всередині

ІМС з'єднані між собою.

Демультиплексор - це логічний пристрій, призначений

для перемикання сигналу з одного інформаційного входу на другий з інформаційних

виходів. Таким чином, демультиплексор у функціональному відношенні протилежний

мультиплексору. На схемах демультиплексоры позначають через DMX або DMS.

У разі ТТЛ логіки для комутації каналів застосовуються

логічні елементи «І». У КМОП мікросхемах широко застосовуються ключі на

польових транзисторах. Тому в них відсутнє поняття демультиплексора.

Інформаційні входи і вихід можна поміняти місцями, в результаті чого

мультиплексор може служити в якості демультиплексора.

Якщо між числом виходів і числом адресних входів

діє співвідношення n=2m для двійкових демультиплексоров або n=3m для трійкових

демультиплексоров, то такий демультиплексор називають повним. Якщо n<2m для

двійкових демультиплексоров або n<3m для трійкових демультиплексоров, то

демультиплексор називають неповним. Функції демультиплексоров схожі з функціями

дешифраторів. Дешифратор можна розглядати як демультиплексор, у якого

інформаційний вхід підтримує напругу виходів в активному стані, а адресні входи

виконують роль входів дешифратора. Тому в позначенні як дешифраторів, так і

демультиплексоров у вітчизняних мікросхемах використовуються однакові літери -

ІД.

Мультипле́ксори - відносяться до пристроїв комутування

цифрової інформації. Вони здійснюють комутацію одного з декількох інформаційних

входів xi до одного виходу y. Мультиплексори мають декілька

інформаційних входів, адресні входи, вхід дозволу мультиплексування (стробуючий

вхід) та один вихід. Кожному з інформаційних входів мультиплексора відповідає

номер, який називається адресою, двійкове число якого подається до адресних

входів. Число інформаційних входів nінф і число адресних входів nадр

зв'язані співвідношенням: nінф=2nадр. Адресний

дешифратор D1, двійковий код у десятковий для керування роботою мультиплексора.

В залежності від

комбінації стану адресних входів а1 та а2 на одному з

чотирьох виходів дешифратора з'являється одиничний потенціал, який дає дозвіл

на спрацьовування відповідної схеми І (D2…D5). Наприклад, при адресному числі

01, коли а1= 1 та а2= 0, на виході 1 дешифратора D1

установлюється рівень логічної одиниці, а на всіх останніх - нульовий. Тому

логічний елемент D3 має дозвіл на спрацьовування. Якщо при цьому на

інформаційному вході x1 діє логічна одиниця, то на виході D3

установлюється 1, а при x1=0 на виході логічного елемента D3 буде

теж нульовий потенціал.

Суматор - пристрій, що перетворює інформаційні сигнали

(аналогові або цифрові) в сигнал, еквівалентний сумі цих сигналів.

Суматор називається функціональний вузол

комп'ютера, призначений для додавання двох н - розрядно слів (чисел). Операція

віднімання замінюється додаванням слів в обернений або доповнювальному коді.

Операціїмноження та ділення перетворюються на реалізації багаторазове додавання

та Зсув. Тому суматор є важливою частиною арифметико - логічного пристрою.

Функція суматора позначається літерами SM або Σ.

Суматори класіфікують за такими ознаками способом

додавання - паралельні, послідовні та паралельно - послідовні; кількістю

вхідніх клем - напівсуматорі, однорозрядні або багаторозрядні суматори.

Напівсуматори - бінарні (двухоперандні) суматори по модулю з

розрядом перенесення, що характеризуються наявністю двох входів, на які

подаються однойменні розряди двох чисел, і двох виходів: на одному реалізується

арифметична сума за модулем в даному розряді, а на іншому - перенесення у

наступний (старший розряд);

Повні суматори - тринарні (трьохоперандні) суматори по модулю з розрядом перенесення, що

характеризуються наявністю трьох входів, на які подаються однойменні розряди

двох чисел, що складаються і перенесення з попереднього (молодшого) розряду, і

двома виходами: на одному реалізується арифметична сума за модулем в даному

розряді, а на іншому - перенесення у наступний (старший розряд). Такі суматори

спочатку орієнтовані тільки на показові позиційні системи числення.

Компаратор (англ. comparator -

порівнюючий пристрій) - електронна схема, яка приймає на свої два аналогових

входи сигналу і видає логічну «1», якщо сигнал на прямому вході («+») більше,

ніж на інверсному вході («-»), і логічний «0», якщо сигнал на прямому вході

менше, ніж на інверсному вході.

Одна напруга порівняння двійкового компаратора

ділить весь діапазон вхідних напруг на два піддіапазони. Двійковий логічний

сигнал (біт) на виході двійкового компаратора вказує, якому з двох

піддіапазонів знаходиться вхідна напруга.

Найпростіший компаратор являє собою

диференціальний підсилювач. Компаратор відрізняється від лінійного операційного

підсилювача (ОУ) пристроєм і вхідного і вихідного каскадів:

Вхідний каскад компаратора повинен витримувати

широкий діапазон вхідних напруг між інвертується і неинвертирующим входами, аж

до розмаху живлячих напруг, і швидко відновлюватися при зміні знака цієї

напруги.

Вихідний каскад компаратора виконується сумісним

по логічним рівням і струмів з конкретним типом входів логічних схем (технологій

ТТЛ, ЕСЛ і т.п.). Можливі вихідні каскади на одиночному транзисторі з відкритим

колектором (сумісність з ТТЛ і КМОП логікою).

Для формування характеристики компаратори часто

охоплюють позитивним зворотним зв'язком. Ця міра дозволяє уникнути швидких

небажаних перемикань стану виходу, обумовленому шумами у вхідному сигналі, при

повільно змінюється вхідному сигналі.

Послідовні схеми

До послідовних схем відносяться різноманітні типи

логічних елементів з двома або більше сталими станами і пристрої на їх основі.

Функції виходів цих пристроїв визначаються не тільки комбінацією діючих

сигналів на вході, але і станом цих виходів до подання вхідних сигналів. До них

відносяться триггери, регістри, лічильники, ОЗП і т.д.

Цифровим лічильником імпульсів називають

послідовний цифровий вузол, який здійснює рахунок надходять на його вхід

імпульсів. Результат рахунку формується лічильником в заданому коді і може

зберігатися необхідний час.

Лічильник кількості імпульсів - пристрій, на виході якого

виходить двійковий (двійково-десятковий код, який визначається числом надійшли

імпульсів. Лічильники можуть будуватися на двоступеневих D-тригерах, T-тригерах

і JK-тригерах.

Лічильники будують на Т-тригерах і ТV-тригерах з

застосуванням при необхідності логічних елементів в ланцюгах міжрозрядні

зв'язків. Кількість тригерів N повинно бути таким, щоб множина внутрішніх

станів лічильника 2N було не менше максимального числа імпульсів, яке повинно

бути зафіксовано. З приходом чергового лічильного імпульсу змінюється стан

лічильника, яке в заданому коді відображає результат рахунку.

Зчитування результату паралельним N-розрядним

кодом може бути здійснене після кожного рахункового імпульсу. Якщо кількість

лічильних імпульсів не обмежувати, то лічильник буде працювати в режимі поділу

їх числа на коефіцієнт (модуль) рахунки Ксч дорівнює 2N. Через кожні 2N

імпульсів він буде повертатися в початковий стан і знову рахувати імпульси.

Ця операція називається поділом, а лічильники,

які її здійснюють, дільниками.

Якщо необхідний коефіцієнт рахунку не дорівнює 2N

застосовують різні способи скорочення числа внутрішніх станів лічильника. Для

побудови лічильника можуть застосовувати не тільки тригери з рахунковим входом,

але і D-тригери, і JК-тригери двоступеневої структури або з динамічним управлінням.

Лічильники можна класифікувати по ряду ознак. За

напрямом рахунки їх ділять на підсумовуючі (з прямим рахунком), вичитающие (із

зворотним рахунком) і реверсивні. В підсумовуючих лічильниках з приходом

чергового лічильного імпульсу результат збільшується на одиницю, в вичитающих -

зменшується на одиницю. Називаються реверсивними лічильники, які можуть

працювати як в режимі підсумкового лічильника, так і в режимі вичитающего

лічильника.

За способом організації переносу розрізняють

лічильники з послідовним, паралельним і комбінованим (паралельно-послідовним)

переносом.

Конструктивно цифрові лічильники можуть бути

виконані у вигляді сукупності інтегральних мікросхем-тригерів певним чином

з'єднаних, і у вигляді однієї мікросхеми підвищеного рівня інтеграції, що

містить сформовану на єдиній основі.

Лічильник - пристрій, на виході якого

виходить двійковий (двійково-десятковий код, який визначається числом надійшли

імпульсів. Лічильники можуть будуватися на двоступеневих D-тригерах, T-тригерах

і JK-тригерах.

Основний параметр лічильника - модуль рахунку -

максимальне число одиничних сигналів, яке може бути сосчитано лічильником.

Лічильники позначають через СТ (від англ. counter).

Регістр (цифрова техніка) - послідовне або

паралельне логічне пристрій, що використовується для зберігання n-розрядних

двійкових чисел і виконання перетворень над ними.

Регістр процесора - надшвидка пам'ять усередині

процесора, призначена для зберігання адрес і проміжних результатів обчислень

(регістр загального призначення/регістр даних) або даних, необхідних для роботи

самого процесора.

Регістр прапорів (FLAGS) - регістр процесора,

біти (прапори) якого відображають стан процесора і властивості результатів

попередніх операцій.

Регістр це

цифровий вузол, який призначений для запису та зберігання коду. Крім

зберігання, деякі види регістрів можуть перетворювати інформацію, наприклад, з

послідовної в часі форми подання в паралельну, зсувати записану інформацію на

один або декілька розрядів в сторону молодшого або старшого розряду, інвертувати

код. У відповідності до призначення розрізняють регістри зберігання.

Важливими характеристиками регістрів є розрядність та

швидкодія. Розрядність залежить від кількості розрядів в числі, яке можна

записати. Швидкодія характеризується максимальною тактовою частотою, з якою

може проводитись запис, зчитування чи зсув інформації.

Регістри зберігання складаються з одноступеневих D - або RS-трігерів. З цією метою

можна також застосовувати і JK-трігери, але їх можливості більші, ніж потрібно для регістру

зберігання. Варіант чотирьохрозрядного регістра зберігання. ІМС К155ТМ8, яка

містить 4 D-трігери з

об'єднаними входами установки нуля та синхронізації. Числа в трігери регістра

записуються по входах D при сигналі дозволу C=1. Після зміни сигналу на вході C

на 0 трігери переходять в режим зберігання. В цей час на входи D можна подати

наступне число, яке при C=1 запишеться в регістр. Для обнулення регістра до

входу R підводять від'ємний імпульс на час, який потрібний для переведення всіх

трігерів. Цей час вказують у довідниках. Поки регістр виконує свої функції, на

вході R підтримується напруга високого рівня

Регістри зберігання, які виконані по різних

варіантах і подані в серіях ІМС широкою номенклатурою, відрізняються

функціональними можливостями, електричними характеристиками, режимами

керування. Багато регістрів мають виходи на три стани і відповідне керування

ними, спеціальні входи для сигналів керування режимом запису, причому деколи

входи керуючих сигналів об'єднані логічним оператором. Ряд серій містить багаторегістрові

ІМС.

2. Побудова принципових схем по булевих виразах

2.1 Функціональна схема

Функціональна схема, яка задана логічною

функцією:

f =

будується в базисі І, АБО, НІ за допомогою программи

Electronics Workbench із застосуванням логічного конвертора. Функціональна

схема містить один інвертор НІ, три двохвходових логічних елемента І та два

двохвходових елемента АБО, зображена на рисунку 1.

Рисунок 1. Функціональна схема

2.2 Принципова схема функції

Принципова схема даної функції реалізована на мікросхемах

серії К155 зображена на рисунку 2.

Рисунок 2. - Принципова схема

На принциповій схемі вказані значення логічних сигналів на

виході кожного логічного елементу для заданої комбінації вхідних сигналів свого

варіанту (x1=0, x2=0, x3=0).

3. Побудова функціональних схем шифратора, дешифратора і

мультиплексора по таблиці істинності

3.1 Функціональних схем шифратора

Рисунок 3 - Умовне графічне позначення дешифратора

Мікросхеми серії К155ИД1, КБ155ИД1-4 та КМ155ИД1 - це

4-розрядні дешифратори призначені для управління газорозрядними індикаторними

лампами. Мікросхема містить 83 інтегральних елемента. Функціональна схема

зображена на рисунку 4.

Рисунок 4 - Функціональна схема дешифратора К155ИД1

Рисунок 5 - Умовне графічне позначення дешифратора К155ИД1

Призначення всіх виводів дешифратора К155ИД1:

- вихід 8;

- вихід 9;

- вхід D1;

- вхід D8;

- напруга живлення (+Uп);

- вхід D2;

- вхід D4;

- вихід 2;

- вихід 3;

- вихід 7;

- вихід 6;

- загальний;

- вихід 4;

- вихід 5;

- вихід 1;

- вихід 0.

Логічний вираз для кожного виходу через операцію І-НІ має

вигляд:=x8’x4’x2’x1’=x8x4x2x1.

3.2

Функціональних схема в базісі І-НІ

Функціональна схема в базисі І-НІ має вигляд

Рисунок 6 - Функціональна схема дешифратора в базісі

І-НІ

4. Розрахунок послідовносної схеми

4.1 Розрахунок лічильника

Лічильник - це пристрій для рахування числа імпульсів.

Число, відображене станом його виходів по фронту кожного

вхідного імпульсу, змінюється на одиницю. Лічильник можна реалізувати на

декількох трігерах.

В підсумовуючих лічильниках кожний вхідний імпульс збільшує число на його

виході на одиницю, в вычитающих лічильниках кожний вхідний імпульс зменшує це

число на одиницю.

Лічильники застосовуються у різних цифрових

пристроях і будуються з розрядних схем, пов'язаних один з одним і містять

трігери і логічні елементи.

У лічильниках виконуються наступні мікрооперації:

встановлення в початковий стан;

- зберігання слова;

видача слова;

збільшення на одиницю вмісту та ін.

Лічильник характеризується насамперед модулем рахунку

(ємністю) N. Він переходить при надходженні вхідних сигналів зі стану в стан,

після кожних N сигналів повертаючись до початку циклу. Лічильники класифікують

за значенням модуля, напрямку рахунки, способом організації межразрядных

зв'язків.

За значенням модуля рахунку розрізняють двійкові (N=2n), двійково-кодовані (з

довільним модулем), з кодування станів двійковими кодами, лічильники з

одинарним кодуванням та ін.

За напрямом рахунку лічильники діляться на підсумовуючі

(прямого рахунку), вычитающие (зворотного рахунку) і реверсивні (зі зміною

напрямку рахунки).

За способом організації межразрядных зв'язків розрізняють

лічильники з послідовним, паралельним і комбінованим переносом. Основними

режимами роботи лічильників є реєстрація числа які надісланих на лічильник сигналів і

ділення частоти.

У першому режимі в лічильнику формується його вміст (цифровий

код), а в другому - вихідними сигналами є імпульси переповнення лічильника.

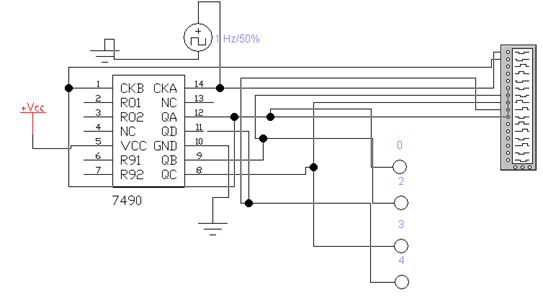

Умовне графічне позначення лічильника К155ИЕ2 зображено на рисунку 7.

Рисунок 7 - Умовне графічне позначення лічильника К155ИЕ2

Призначення всіх виводів лічильника К155ИЕ2:

- лічильний вхід С2; 2 - вхід установки 0 R0 (1);

- вхід установки 0 R0 (2); 4,13 - вільні;

- напруга живлення +Uж; 6 - вхід установки 9 R9 (1);

- вхід установки 9 R9 (2); 8 - вихід Q3;

- вихід Q2; 10 - загальний;

- вихід Q4; 12 - вихід Q1;

- лічильний вхід C1

Визначення розрядності лічильника (n) і

коефіцієнта перерахунку (N).

Мікросхеми К155ИЕ2 і КМ155ИЕ2 (7490) чотирирозрядний

десятковий асинхронний лічильник пульсацій. Внутрішня схема його показана на

малюнку. Перший трігер лічильника DD1.3 може працювати самостійно. Він служить

дільником вхідної частоти в 2 рази, Тактовий вхід цього дільника C0 (вивід 14),

а вихід QO (висновок 12). Інші три трігера DD1.4 - DD1.6 утворюють дільник на 5.

Тактовий вхід тут C1 (висновок 1). Для обох тактових входів запускає перепад

негативний, тобто від високого рівня до низького.

Лічильник має два входи R для синхронного скидання (висновки

6 і 7), а також два синхронних входу S (висновки 2 і 3) для попереднього

завантаження в лічильник двійкового коду 1001, відповідного десятковій цифрі 9.

Оскільки лічильник К155ИЕ2, КМ155ИЕ2 (7490) асинхронний, стану на його виходах

Q0 - Q3 не можуть змінюватися одночасно.

Функціонална схема

лічильника К155ИЕ2.

Рисунок 8 - Схема лічильника К155ИЕ2

Якщо мікросхема К155ИЕ5, КМ155ИЕ5 (7493) застосовується як

лічильник-дільник на 16, необхідно з'єднати виводи 1 і 12. При цьому

послідовність рахунку від 0 до 15 (тобто послідовність зміни логічних рівнів на

виходах Q1 - Q4) буде відповідати таблиці. Інші особливості застосування

лічильника К155ИЕ5 відповідають мікросхем ИЕ2 і ИЕ4. Мікросхема К155ИЕ5 (аналог

7493) споживає струм 53 мА і працює з тактовою частотою 10 МГц. Лічильник

74LS93 споживає струм 15 мА, по входу ЗІ максимальна частота до 10 МГц і по

входу C1 32 МГц.

Таблиця 3 - З'єднання виводів для зміни К

|

К

|

К155ИЕ2

|

К155ИЕ4

|

К155ИЕ5

|

|

Вход

|

Вих.

|

Зеднать входов

|

Вход

|

Вих.

|

Вход

|

Вих.

|

Зеднать входов

|

|

2

|

14

|

12

|

|

14

|

12

|

-

|

14

|

12

|

-

|

|

3

|

1

|

8

|

9-2,8-3

|

1

|

9

|

-

|

1

|

8

|

9-2,8-3

|

|

4

|

1

|

8

|

11-2-3

|

1

|

8

|

11-6,8-7

|

1

|

8

|

-

|

|

5

|

1

|

11

|

-

|

1

|

8

|

9-6,8-7

|

1

|

11

|

9-2,11-3

|

|

6

|

14

|

8

|

12-1,9-2,8-3

|

1

|

8

|

-

|

1

|

11

|

8-2,11-3

|

|

7

|

14

|

11

|

12-1,9-6,8-7

|

14

|

8

|

12-1-6,8-7

|

-

|

-

|

-

|

Значення логічних сигналів

Вкажіть на УГП значення логічних сигналів, які

слід подати на входи лічильника для попереднього запису в лічильник двійкового

числа (коду) 0100, заданого в таблиці 3.

Рисунок 9 - Функціональна схема лічильника К155ИЕ2

Рисунок 10 - Часова діаграма лічильника К155ИЕ2

Розрахунок двійкового коду

Виконайте розрахунок і вкажіть на виходах УГП

двійкове число (код) в режимі рахунку (складання) після надходження заданого

числа тактових (вхідних) імпульсів, якщо заздалегідь в ньому було записане

задане двійкове число 60 (див. таблицю 5 завдання).

Коли кратне 10 то ми через 60 імпульсів отримаємо теж саме

число

(0100)

Зарубежным аналогом счётчиков К155ИЕ2, КМ155ИЕ2 являеться мікросхема 7490.

4.2 Розрахунок регістру

Виберіть з таблиці 6 мікросхему регістра для

свого варіанту.

Мікросхема К555ИР12 - миогорежимиый буферний регістр (МБР), є

універсальним 8-разрядиым регістром з виходами, що мають три стани. Він має

вбудовану логічну схему та незалежний трігер для формування запиту на

переривання центрального процесора. Одні або кілька МБР можуть

використовуватися для реалізації багатьох типів інтерфейсних та допоміжних

пристроїв, включаючи: прості регістри даних; буферні регістри зі стробированием

даних; мультиплексори; двонаправлені шиииые формувачі; прерываемые канали вводу

/ виводу та ін.

Приведіть (побудуйте) умовне графічне позначення

(УГП) вибраного

регістра.

Рисунок 11 - Умовне графічне позначення регістра

К555ИР12

Мікросхема складається з восьми інформаційних D-трігерів, восьми

вихідних буферних пристроїв з трьома стійкими станами, окремого D-трігера для формування

запитів на переривання і гнучкої схеми керування режимами роботи регістра.

Таблиця 4 - Призначення всіх виведень регістра

Інформаційні D-трігери повторюють вхідну інформацію при

високому рівні вхідного сигналу MDи (CS1 - CS2) = 1, а також при EW=1 і MD=0, при низькому рівні

сигналу на вході EWи (CS1 - CS2)=1 при MD=0 відбувається зберігання вхідної інформації. Виходи кожного

інформаційного трігера

з'єднані з вихідними буферними каскадами з трьома стійкими станами. Внутрешня шина видачі інформації

РВ стробує кожен вихідний буферний каскад. При наявності лог. 1 на шині РВ вихідні буферні

каскади розблоковані і дані надходять на вихід відповідної лінії вихідних даних (Q1-Q8).

Умова вироблення появи сигналу PB=MDV CS1-CS2. Внутрешня шина запису інформації

Wстробіруе кожен трігер регістра. При

наявності лог. 1 на шині відбувається запис інформації в трігер з відповідних

вхідних інформаційних шин (D1-D8). Умова появи сигналу: W=EW ٨

MDV

MD-CS1*XCS2. Інформація в трігерах МБР обнуляється асинхронно вхідним сигналом CLR.

У МБР керуючими входами є CS1, CS2, MDи EW. Ці входи

використовуються для управління вибіркою пристрою, інформацією регістру, станом

вихідних буферних каскадів і трігером запиту на переривання.

Вибіркою кристала керують входи CS1 і CS2. При наявності лог. 0

іа вході CS1 н лог. 1 іа

вході CS2 пристрій

обрано. Сигнал вибірки кристала (CS1, CS2) використовується як синхросигнал для

асинхронної установки стану вихідних буферних каскадів регістра і трігера

запиту переривання.

Вхід MD (вибір режиму) визначає одні з двох режимів роботи.

При наявності лог. На вході MDустройство працює в режимі введення. У цьому

режимі, вихідні буферні каскади відкриті, коли пристрій обрано. Управління

записом здійснюється сигналом по входу EW.

При наявності лог. 1 на вході MD пристрій працює в режимі

виводу. У цьому випадку вихідні буферні каскади відкриті незалежно від вибірки

пристрою.

Вхід EW використовується як синхросигнал для запису

інформації в регістр при MD = 0 і для синхронної установки трігера запиту переривання.

Трігер запиту переривання служить для вироблення сигналу запиту

переривання в процесорній системі. При установці системи в початковий стан

инзким рівнем сигналу CLRтриггер запиту переривання встановлюється в 1, тобто

даний пристрій ие вимагає переривання. Одночасно цим же сигналом відбувається

установка регістра в 0. Прийнято, що МБР знаходиться в стані переривання, коли

виходу INRсоответствует лог. 0, що дозволяє забезпечити пряме сполучення з

входами запиту блоку пріоритетного переривання. При роботі в режимі введення

(тобто іа вході MDсигнал низького рівня) вхідний сигнал EWпроизводит запис

інформації в регістр даних і встановлення трігера запиту 0. Трігер запиту переривання

встановлюється в 1 за умови вибору пристрою (також виробляється сигнал

переривання на виході 1NR).

Зарубіжним аналогом лічильника К555ИР12, К555ИР16 являється мікросхема

74295.

5. Побудова схеми

5.1 Побудувати дешифратор на 32 виходи на основи

мікросхем серії 155

З мікросхем комбінаційного типу при розробці цифрових пристроїв

широко використовують дешифратори, їх номенклатура досить різноманітна.

Мікросхема К155ИД3 (рис. 12) має чотири адресних входу 1, 2, 4, 8,

два інверсні входи стробування S, об'єднаних за І, і 16 виходів 0-15.

Якщо на обох входах стробування лог. 0, тому з виходів, номер

якого відповідає десятичному еквіваленту вхідного коду (вхід 1 - молодший

розряд, вхід 8-старший), буде лог. 0, на інших виходах - лог. 1. Якщо хоча б на

одному з входів стробування S лог. 1, то незалежно від станів входів на всіх

виходах мікросхеми формується лог. 1.

Рисунок 12 - Мікросхема К155ИД3

Наявність двох входів стробування істотно розширює можливості

використання мікросхем. З двох мікросхем ИДЗ, доповнених одним інвертором,

можна зібрати дешифратор на 32 виходи (рис. 13).

Рисунок 13 - Дешифратор на 32 виходи

Висновок

В курсовій рооті було розглянуто основні теоретичні

принципи роботи комбінаційних та послідовних схем. Описані основні принципи

розраховуваних схем згідно варіанту. Виконані розрахунки: принципової схеми по

булевому виразу, дешифратора, лічильника, регістру, дешифратору на 32 входи, на

основі мікросхем серії К155.

Список літератури

комп'ютерний шифратор мультиплексор схема

1) ЕСКД.

Основні положення. М.: Видавництво стандартів, 1984,343 с.

2) ЕСКД.

Позначення умовні графічні в схемах. М.: Видавництво стандартів, 1983,496 с.

) Єдина

система програмної документації. М.: Видавництво стандартів, 1985,128 с.

) ЕСКД.

Загальні правила виконання креслень. М.: Видавництво стандартів, 1984,239 с.

) ЕСКД.

ДСТ2.701-84 (СТ СЭВ 651-77) Схеми. Види і типи. Загальні вимоги до виконання.

) ЕСКД.

ДСТ2.702-75 Правила виконання електричних схем.

) ЕСКД.

ДСТ2.709-72 (СТ СЭВ 3754-82) Системи позначення ланцюгів в електричних схемах.

) ДСТ7.32-81

Звіт про науково дослідницьку роботу. Загальні вимоги і правила оформлення.

) ДСТ

10317-79 Друковані плати.

) ДСТ

17021-75 Мікросхеми інтегральні. Терміни і визначення.

) ДСТ

17467-79 Мікросхеми інтегральні. Основні розміри.

) ДСТ

10318-80 Значення номінальних опорів.

) ДСТ

10862-72 Позначення напівпровідникових приладів.

) ДСТ2.170-81

Позначення буквено-цифрові в електричних схемах.

) Воробьев

Н.И. Проектирование электронных устройств. - М.; Высшая школа. 1989. - 231 с.

) Бабіч

М.П., Жуков І.А. Комп’ютерна схемотехніка: Навчальний посібник. - К.:

«МК-Прес», 2004. - 412 с.

) Матвієнко

М.П., Розен В.П. Комп’ютерна схемотехніка: Навчальний посібник. - К.: Ліра-К,

2013. - 192 с.

) Угрюмов

Е.П. Цифровая схемотехника СПб: БХВ-Петербург, 2001

) Рябенький

В.М., Жуйков В.Я., Гулий В.Д. Цифрова схемотехніка: Навчальний посібник. Львів:

«Новий Світ-2000», 2009.

) Сергиенко

А.Б. Цифровая обработка сигналов СПб: Питер, 2003

) Компьютерная

схемотехника (краткий курс). / Процюк Р.О., Корнейчук В.И., Кузьменко П.В.,

Тарасенко В.П. - К.: «Корнійчук», 2006. - 433 с.

) Голубенко

Г.О., Кафтан Ю.М. Комп’ютерна схемотехніка Миколаїв: МПІ, 2012 ел. підручник

) Бойко

В.И. и др. Схемотехника электронных систем. Цифровые устройства. - СПб.:

БХВ-Петербург, 2004. - 512 с.

) Сергиенко

А.М., Микропроцессорные устройства на программируемых логических ИС. /Сергиенко

А.М., Корнейчук В.И. - К.: «Корнійчук», 2005. - 108 с.