Тактирующие устройства. Триггеры

ЮЖНО - КАЗАХСТАНСКИЙ ПОЛИТЕХНИЧЕСКИЙ

КОЛЛЕДЖ

КУРСОВОЙ ПРОЕКТ

По дисциплине: Микросхемотехника

На тему: Тактирующие устройства.

Триггеры

Студент

группы 414к ____________ Худоерко С.В.

Преподаватель

_____________ Алтынова Б.Л.

Шымкент 2013 г

«Утверждаю»

Заведующий кафедры электроники

и информационных систем

__________ Бакбергенов К.Ж.

«____» _________2013г.

ЗАДАНИЕ

на курсовой

проект

Студента: Худоерко С.

Специальности: 1304033 «Вычислительные машины, комплексы,

системы и сети»

Тема проекта: Тактирующие устройства. Триггеры.

Исходные данные: Произвести исследование и анализ тактирующим устройствам

и триггерам.

Описать математические модели триггера

Дата выдачи курсового проекта « » 2013 г

Срок сдачи курсового проекта « » 2013 г

Расчетно-пояснительная записка

Студент: Худоерко Сергей

Руководитель курсового

проектирования: Алтынова Багила Лесовна

По основной части: ___________________

По специальной части: ___________________

Приложение:

Графическая часть на ______________________ листах

Содержание

Введение

. Триггеры

.1 Общие сведения

.2 Назначение триггера

.3 Основные обозначения

.4 Физическая реализация триггеров

. Типы триггеров

.1 Асинхронные триггеры

.1.1 RS-триггер с инверсными входами

.2 Синхронные триггеры

.2.1 RS-триггер

.2.2 D-триггер

.3 Синхронные триггеры, построенные по принципу

двухступенчатого запоминания информации

.3.1 JK-триггер

.3.2 Т-триггер

.3.3 D-триггер

.3.4 T-триггер(обратная схема)

.3.4 JK-триггep

. Математическое моделирование триггера в приложении

Electronics Workbench (Специальная часть)

Заключение

Список используемой литературы

Приложение (Графическая часть)

Введение

Данная работа посвящена рассмотрению роли триггеров в цифровых

устройствах.

Во всех современных компьютерах применяется логическая система,

изобретения Джорджем Булем.

С развитием электроники появился такой класс электронной техники, как

цифровая. Цифровая техника включает в себя такие устройства как триггеры,

регистры, счётчики, комбинационные устройства, программируемые логические интегральные

схемы и др.

Средством обработки двоичных сигналов в ЭВМ являются логические элементы.

Логический элемент компьютера - это часть электронной логической схемы с

одним или несколькими входами и одним выходом, черех которую проходят

электрические сигналы, представляющие 0, 1.

К таким устройствам относятся такие типовые логические устройства как

триггер, сумматор, полусумматор, шифратор, дешифратор и счётчик. Они

предназначены для формирования, обработки и передачи электрических импульсных

сигналов и перепадов напряжения и тока, а также для управления информацией и её

хранения одном бите, то

есть 0 или 1.

Целью данной работы является рассмотрение триггеров применяемых в ЭВМ,

как они устроены и функционируют.

Объектом исследования данной работы стали триггеры, в состав которых

входят: RS-, D-, T- и

JK-триггеры.

Курсовое исследование написано при использовании специализированных

исследований некоторых авторов. Библиографический список представлен в конце

курсовой работы.

.ТРИГГЕРЫ

1.1 Общие сведения

Интегральные триггеры обычно реализуются на логических элементах И-НЕ,

ИЛИ-НЕ. Обратимся к таблицам истинности функции, реализуемых логическими

элементами И-НЕ и ИЛИ-НЕ (табл.1). Легко убедиться, что каждый из этих

элементов характеризуется некоторым логическим уровнем (лог. 0 или 1), действие

которого на одном из входов полностью определяет логический уровень на выходе.

При этом логический уровень на выходе элемента не изменяется, какие бы

комбинации логических уровней ни подавались на другие входы этого элемента.

Такими логическими уровнями для элементов И-НЕ является уровень лог. 0, для

ИЛИ-НЕ - уровень лог. 1.

Действительно, если на один из входов элемента И-НЕ подан лог. 0, то на

выходе этого элемента возникает лог. 1 независимо от того, каковы логические

уровни на других входах; лог. 1, поданная на один из входов элемента ИЛИ-НЕ,

установит на выходе уровень лог. 0, который не будет зависеть от логических

уровней, действующих на других входах элемента.

Такие логические уровни, которые, действуя на одном из входов элемента,

однозначно задают логический уровень на его выходе независимо от уровней на

других входах, будем называть активными логическими уровнями. Таким образом,

активный логический уровень для элементов И-НЕ - уровень лог. 0, для элементов ИЛИ-НЕ

- уровень лог. 1.

Так как при подаче активного логического уровня на один из входов

элемента он и определяет уровень на выходе элемента (выходной уровень элемента

при этом не зависит от уровней на других входах), можно говорить, что при этом

происходит логическое отключение остальных входов элемента.

Уровни, обратные активным, будем называть пассивными логическими

уровнями. Пассивными уровнями для элементов И-НЕ служит уровень лог. 1, для

ИЛИ-НЕ - уровень лог. 0. При действии на одном из входов пассивного логического

уровня уровень на выходе элемента определяется логическими уровнями на других

его входах.

Пользование понятиями активного и пассивного логических уровней облегчает

анализ функционирования триггеров, построенных на элементах И-НЕ при ИЛИ-НЕ.

1.2 Назначение триггера

Воздействуя на входы триггера, его устанавливают в нужное состояние.

1.3 Основные обозначения

Триггер имеет два выхода: прямой Q и инверсный  . Уровнями напряжения на этих выходах

определяется состояние, в котором находится триггер: если напряжение на выходе

Q соответствует уровню лог. 0 (Q = 0), то принимается, что триггер находится в

состоянии лог. 0, при Q = 1 триггер находится в состоянии лог. 1. Логический

уровень на инверсном выходе

. Уровнями напряжения на этих выходах

определяется состояние, в котором находится триггер: если напряжение на выходе

Q соответствует уровню лог. 0 (Q = 0), то принимается, что триггер находится в

состоянии лог. 0, при Q = 1 триггер находится в состоянии лог. 1. Логический

уровень на инверсном выходе  представляет собой инверсию состояния триггера (в состоянии 0

Q = 1 и наоборот).

представляет собой инверсию состояния триггера (в состоянии 0

Q = 1 и наоборот).

Триггеры имеют различные типы входов. Приведем обозначение и назначение

входов триггеров:(от английского RESET) - раздельный вход установки в состояние

0;(от английского SET) - раздельный вход установки в состояние 1;- вход

установки универсального триггера в состояние 0;- вход установки универсального

триггера в состояние 1;- счетный вход;(от английского DELAY) - информационный

вход установки триггера в состояние, соответствующее логическому уровню на этом

входе;- управляющий (синхронизирующий) вход.

Наименование триггера определяется типами его входов. Например,

RS-триггер - триггер, имеющий входы типов R и S.

По характеру реакции на входные сигналы триггеры делятся на два типа:

асинхронные и синхронные. Асинхронный триггер характеризуется тем, что входные

сигналы действуют на состояние триггера непосредственно с момента их подачи на

входы, в синхронных триггерах - только при подаче синхронизирующего сигнала на

управляющий вход С.

1.4 Физические реализации триггеров

Триггеры с тиристорами

Тиристор подходит для замены элемента памяти в триггерах.

Описание схемы на примере RS триггера: К катоду тиристора подключается

выход триггера Q, к управляющему электроду подключается вход S, к аноду

подключается постоянное напряжение через полевой транзистор с изолированным

затвором, к затвору полевого транзистора подключается вход R.

Описание работы: Начальное состояние на выходе Q ноль: тиристор находится

в замкнутом состоянии, ток на выходе соответствует нулю. Переход в состояние

единица: на вход S подается напряжение равно логической единице тиристор

разблокируется и напряжение на выходе Q повышается соответственно логической

единице, при последующем понижении напряжения на входе S тиристор сохраняет

низкое сопротивление и напряжение на выходе Q остается равным логической

единице. Переход от логической единицы к нулю: на вход R подается напряжение

равное логической единице полевой транзистор переходит в замкнутое состояние,

напряжение на аноде тиристора падает, вследствие чего сопротивление тиристора

возрастает и он переходит в состояние низкого выходного напряжения

соответствующего логическому нулю, это состояние сохраняется при повышении

входного напряжения на аноде тиристора.

Тиристор можно заменить на два биполярных транзистора (смотря какая

реализация будет удобнее).

Как итог мы получаем RS триггер на трех транзисторах.

Триггеры на релейно - контакторной базе

Несмотря на развитие электроники и особенно микроэлектроники до сих пор

применяется простая логика на электромагнитных реле. Это связано с

исключительной простотой реализацией таких схем, помехоустойчивостью ( т.к.

электромагнитные реле потребляют в большинстве своём значительный ток и поэтому

для сбоев таких схем необходима очень большая помеха, что на практике почти не

реализуемо ) и огромным сопротивлением между входом и выходом ( почти идеальная

развязка ) и практическим отсутствием отладки собранной схемы. Всё это приводит

к самым минимальным затратам по времени на разработку систем автоматики, не

требующей особого быстродействия и сложного алгоритма.

2.Типы триггеров

Рассмотрим общие характеристики основных типов триггеров. Каждый тип

триггера характеризует таблица переходов (табл. 1).

|

Таблица 1

|

|

а)

|

|

б)

|

|

S

|

R

|

Q

|

|

J

|

K

|

Q

|

|

0

|

0

|

Q0

|

|

0

|

0

|

Q0

|

|

0

|

1

|

0

|

|

0

|

1

|

0

|

|

1

|

0

|

1

|

|

1

|

0

|

1

|

|

1

|

1

|

*

|

|

1

|

1

|

0 0

|

|

в)

|

|

г)

|

|

D

|

Q

|

|

T

|

Q

|

|

0

|

1

|

|

0

|

Q0

|

|

1

|

1

|

|

1

|

0 0

|

Таблица переходов (табл. 1,а) соответствует работе RS-триггера. Здесь Q0

- текущее состояние триггера (состояние до подачи на вход активного сигнала).

При отсутствии на входах R и S активного уровня триггер сохраняет текущее

состояние Q0. Активный сигнал R = 1 устанавливает триггер в состояние 0, а

сигнал S = 1 - в состояние 1. Звездочкой в таблице отмечено состояние,

соответствующее запрещенной комбинации входных сигналов.

Таблица 1,б является таблицей переходов JK-триггера. Этот тип триггера

отличается от RS-триггера отсутствием запрещенной комбинации входных сигналов,

при J = K = 1 триггер устанавливается в состояние, противоположное текущему

состоянию Q0.

Таблица 1,в является таблицей переходов D-триггера. Триггер устанавливается

в состояние, соответствующее уровню сигнала на входе 0.

Таблица 1,г определяет работу Т-триггера. При входном сигнале Т = 0

триггер сохраняет текущее состояние Q0, при входном сигнале Т = 1 триггер

переключается в состояние, противоположное текущему.

2.1 Асинхронные триггеры

RS-триггер с прямыми входами. Логическая структура триггера представлена

на рис. 1,а. Триггер построен на двух логических элементах ИЛИ-НЕ, связанных

таким образом, что выход каждого элемента подключен к одному из входов другого.

Такое соединение элементов в устройстве обеспечивает два устойчивых состояния,

в чем легко убедиться.

Пусть на входах R и S действуют пассивные для элементов ИЛИ-НЕ уровни

лог. 0, которые не влияют на состояние триггера. В состоянии 0 триггера на

выходе элемента A Q = 0; этот уровень подается на вход элемента B, при этом на

обоих входах элемента B действует уровень лог. 0 и на выходе элемента  = 1; с выхода элемента В уровень лог.

1 поступает на вход элемента А, что и обеспечивает на его выходе уровень 0. Это

одно из устойчивых состояний триггера. В состоянии 1 триггера на выходе

элемента А Q = 1, что обусловливает на выходе элемента В

= 1; с выхода элемента В уровень лог.

1 поступает на вход элемента А, что и обеспечивает на его выходе уровень 0. Это

одно из устойчивых состояний триггера. В состоянии 1 триггера на выходе

элемента А Q = 1, что обусловливает на выходе элемента В  = 0, при этом на обоих входах

элемента А действуют уровни 0, что и обеспечивает на выходе этого элемента

уровень лог, 1. Таким образом, в каждом из состоянии триггера элементы А и В

оказываются в противоположных состояниях.

= 0, при этом на обоих входах

элемента А действуют уровни 0, что и обеспечивает на выходе этого элемента

уровень лог, 1. Таким образом, в каждом из состоянии триггера элементы А и В

оказываются в противоположных состояниях.

Под действием уровня R = 1 элемент А установится в состояние, при котором

на его выходе Q = 0, следовательно, на инверсионном выходе  = 1, и, таким образом, триггер

устанавливается в состояние 0. Если триггер и прежде, до подачи сигнала R = 1,

находился в состоянии 0, то его состояние не изменяется. Если же триггер

находился в состоянии 1, то при подаче сигнала R = 1 произойдет переключение

элемента А и на его выходе установится уровень Q = 0; далее этот уровень,

действуя на входе элемента К, переключит его и на выходе элемента В установится

уровень Q = 1 , после чего триггер оказывается установленным в состояние 0.

Таким образом, при переключении триггера из одного состояния в другое его

элементы последовательно переключаются и время переключения равно удвоенному

среднему времени задержки распространения сигнала в логическом элементе ИЛИ-НЕ:

= 1, и, таким образом, триггер

устанавливается в состояние 0. Если триггер и прежде, до подачи сигнала R = 1,

находился в состоянии 0, то его состояние не изменяется. Если же триггер

находился в состоянии 1, то при подаче сигнала R = 1 произойдет переключение

элемента А и на его выходе установится уровень Q = 0; далее этот уровень,

действуя на входе элемента К, переключит его и на выходе элемента В установится

уровень Q = 1 , после чего триггер оказывается установленным в состояние 0.

Таким образом, при переключении триггера из одного состояния в другое его

элементы последовательно переключаются и время переключения равно удвоенному

среднему времени задержки распространения сигнала в логическом элементе ИЛИ-НЕ:

t пер = 2t зад. р. ср. (1)

Очевидно, чем меньше t пер, тем большее число переключений триггера

удастся произвести в единицу времени, т.е. будет выше допустимая частота

переключений или, иначе говоря, быстродействие триггера.

Процесс установки триггера в состояние 1 при подаче на вход S уровня лог.

1 аналогичен описанному.

Одновременная подача активных уровней 1 на оба входа R и S не

допускается, так как при этом на обоих выходах установится уровень 0, а после

снятия со входов активных уровней состояние триггера окажется неопределенным: в

силу случайных причин триггер может установиться в состояние 0 либо 1. На рис.

1,б приведена таблица состояний RS-триггера в форме таблицы Вейча. Из этой

таблицы может быть построено логическое выражение, определяющее

функционирование RS-триггера:

(2)

(2)

т.е. триггер устанавливается в состояние 1 под действием входного уровня

S = 1 либо остается в этом состоянии 1, если R = 0 и прежнее состояние триггера

Q0 = 1.

На рис. 1,в показано условное обозначение асинхронного RS-триггера.

2.1.1 RS-триггер с инверсными входами

Логическая структура триггера приведена на рис.2,а. Отличие от логической

структуры рассмотренного выше RS-триггера с прямыми входами состоит лишь в том,

что здесь использованы логические элементы И-НЕ.

При этом активным логическим уровнем на входах является уровень лог. 0,

пассивным - лог. 1. Для того чтобы активными были, как и в предыдущем триггере,

входные сигналы S = 1 и R=1, будем считать, что на входы подаются инверсии  и

и  . Тогда при S = 1 (или R = 1)

. Тогда при S = 1 (или R = 1)  = 0 (или

= 0 (или  = 0) и на входе триггера будет

действовать активный уровень лог. 0. Другое удобство такого обозначения входных

величин состоит в том, что триггер с инверсными входами описывается той же

таблицей состояний (рис. 1.б), что и триггер с прямыми входами.

= 0) и на входе триггера будет

действовать активный уровень лог. 0. Другое удобство такого обозначения входных

величин состоит в том, что триггер с инверсными входами описывается той же

таблицей состояний (рис. 1.б), что и триггер с прямыми входами.

Рассмотрим устойчивые состояния триггера. Пусть на входах действуют

пассивные уровни S = 0 и R = 0 ( = l и

= l и  = 1). В состоянии 0 триггера Q = 0, этот уровень передается

на вход элемента В и вызывает на его выходе уровень Q = l, уровень 1 с выхода

элемента В подается на вход элемента А, и так как на обоих входах элемента А

уровень 1, то на выходе этого элемента Q = 0. Аналогично определяется второе

устойчивое состояние триггера.

= 1). В состоянии 0 триггера Q = 0, этот уровень передается

на вход элемента В и вызывает на его выходе уровень Q = l, уровень 1 с выхода

элемента В подается на вход элемента А, и так как на обоих входах элемента А

уровень 1, то на выходе этого элемента Q = 0. Аналогично определяется второе

устойчивое состояние триггера.

При подаче активного уровня  = 0 (S = 1) на выходе элемента А

устанавливается уровень Q = l, на выходе элемента В - уровень

= 0 (S = 1) на выходе элемента А

устанавливается уровень Q = l, на выходе элемента В - уровень  = 0 и триггер оказывается

установленным в состояние 1. При подаче активного уровня

= 0 и триггер оказывается

установленным в состояние 1. При подаче активного уровня  = 0 (R = 1) триггер устанавливается в

состояние 0. Как и для триггера с прямыми входами, одновременная подача

активных уровней на оба входа не допускается.

= 0 (R = 1) триггер устанавливается в

состояние 0. Как и для триггера с прямыми входами, одновременная подача

активных уровней на оба входа не допускается.

На рис. 2,б показано условное обозначение RS-триггера с инверсными

входами.

2.2 Синхронные триггеры со статическим управлением

Рассмотрим триггеры, в которых действие управляющих сигналов на входе С

проявляется в течение всего времени существования этих сигналов.

2.2.1 RS-триггер

На рис. 3,а,б показаны логические структуры синхронного RS-триггера. Как

видно из представленных структур, синхронный RS-триггер состоит из асинхронного

триггера с прямыми (либо инверсными) входами, на входах R и S которого включены

логические элементы И (И-НЕ). С помощью логических элементов И (H-HE)

обеспечивается передача активных уровней информационных входов S и R синхронного

триггера на входы S и R входящего в его состав асинхронного триггера только при

наличии уровня лог. 1 на синхронизирующем входе С.

Таким образом, при C = 0 на входы асинхронного триггера не передаются

активные уровни и триггер сохраняет ранее установленное в нем состояние Q0. При

C = l состояние триггера определяется действующими на входах уровнями так же,

как и в рассмотренном выше асинхронном RS-триггере, Следовательно,

функционирование синхронного RS-триггера может быть описано логическим

выражением

(3)

(3)

Нормальная работа синхронного RS-триггера требует, чтобы за время

действия лог. 1 на синхронизирующем входе С уровни на информационных входах S и

R оставались неизменными. Смена уровней на входах допускается лишь в то время,

когда C = 0 и триггер не реагирует на уровни, действующие на входах S и R.

На рис. 3,в показано условное изображение синхронных RS-триггеров в

схемах.

2.2.2 D-триггер.

Имеет лишь один информационный вход, называемый входом D, Вход С

управляющий и служит для подачи синхронизирующего сигнала.

Функционирование D-триггера определяется таблицей состояний (рис. 4,а).

Как видно из таблицы, при C = l триггер устанавливается в состояние,

определяемое логическим уровнем на входе D (при C = 0 он сохраняет ранее

установленное состояние Q0). Такое функционирование может быть описано

логическим выражением

(4)

(4)

На рис.4,б представлены логические структуры D-триггера, состоящего из

асинхронного RS-триггера с логическими элементами на входах. При C = 0 на

выходах элементов И (И-HE) образуются пассивные для входов асинхронного

RS-триггера уровни. При C = l уровень, поданный на информационный вход D,

создает активный уровень либо на входе R (при D = 0) либо на входе S (при D =

l) асинхронного RS-триггера, и триггер устанавливается в состояние,

соответствующее логическому уровню на входе D). Таким образом, D-триггер

воспринимает информацию со входа D при C = l и затем ее может хранить

неопределенно длительное время, пока C = 0. На рис. 4,г показано символическое

изображение D-триггера.

2.3 Синхронные триггеры, построенные по принципу двухступенчатого

запоминания информации

Особенность триггеров с двухступенчатым запоминанием информации состоит в

том, что они содержат две триггерные структуры: одна из них образует так

называемый ведущий триггер а другая - ведомый (рис.5) . Оба триггера

функционируют как синхронные триггеры со статическим управлением. При значении

на синхронизирующем входе С = 1 ведущий триггер устанавливается в состояние,

соответствующее сигналам, поступающим на информационные входы. Ведомый триггер,

имеющий инверсный синхронизирующий вход при этом невосприимчив к информации,

поступающей на его вход с выхода ведущего триггера. Он продолжает находиться в

состоянии, в которое был ранее установлен (в предыдущем тактовом периоде).

При изменении значения С (с значения С = 1 на значение C = 0) ведущий

триггер отключается от информационных входов и перестает реагировать на

изменения значений сигналов на этих входах; ведомый триггер устанавливается в

состояние, в котором находится ведущий триггер. С этого момента на выходах

устанавливаются значения, соответствующие входным сигналам, поступавшим к

моменту рассматриваемого фронта сигнала на синхронизирующем входе.

Таким образом, управление процессами в триггере с двухступенчатым

запоминанием информации за время тактового периода осуществляется двумя

фронтами сигнала на синхронизирующем входе: на положительном фронте происходят

установка ведущего триггера, на отрицательном фронте - ведомого триггера. В

качестве примера рассмотрим JK-триггep с двухступенчатым запоминанием

информации.

2.3.1 JK-триггер

На рис. 6 таблица состояний JK-триггера представлена в форме диаграммы

Вейча, из которой можно получить следующее логическое выражение, определяющее

функционирование JK-триггера:

(5)

(5)

Из (5) следует, что состояние Q, в которое устанавливается триггер,

определяется не только уровнями на информационных входах J и K, но и состоянием

Q0, в котором ранее находился триггер. Это определяет возможность построения

логической структуры JK-триггера с использованием двух RS-триггеров. Один из

RS-триггеров (ведомый) предназначен для хранения текущего состояния Q0;

снимаемые с его выходов уровни Q0 и  0 совместно с информационными

сигналами входов J и К используются для формирования нового состояния Q в

другом RS-триггере (ведущем), JK-триггер с подобной логической структурой

представлен на рис. 7,а. Так как каждый из триггеров совместно с элементами И

на входах образует схему синхронного RS-триггера, то логическая структура может

быть такой, как показано на рис. 7,б. Здесь ведущий триггер Тг1, имеет по две

пары связанных операцией И входов J и К.

0 совместно с информационными

сигналами входов J и К используются для формирования нового состояния Q в

другом RS-триггере (ведущем), JK-триггер с подобной логической структурой

представлен на рис. 7,а. Так как каждый из триггеров совместно с элементами И

на входах образует схему синхронного RS-триггера, то логическая структура может

быть такой, как показано на рис. 7,б. Здесь ведущий триггер Тг1, имеет по две

пары связанных операцией И входов J и К.

При уровне лог. 0 на входе С триггер Тг1, не реагирует на сигналы входов

J и К. На синхронизирующий вход триггера Тг2 при этом подается уровень лог. 1,

и состояние ведущего триггера Тг1 передается ведомому триггеру Тг2. Оба

триггера оказываются в одном и том же состоянии. При переходе на входе С к

уровню лог. 1 на синхронизирующий вход триггера Тг2 через инвертор подается

уровень лог. 0 и логическая связь между триггерами обрывается. Триггер Тг1

устанавливается в состояние Q, определяемое выражением (5). Подача вновь на

вход С уровня лог. 0 приводит к передаче состояния Q из триггера Тг1, в триггер

Тг2. Символическое изображение описанного JK-триггера приведено на рис. 7,в.

На рис. 8 показано включение JK-триггера, при котором он выполняет

функции D-триггера.

2.3.2 Т-триггер

На рис. 9,а показана логическая структура Т-триггера. При поступлении на

вход Т импульса на положительном его фронте ведущий триггер Тг1,

устанавливается в состояние, противоположное состоянию ведомого триггера Тг2;

на отрицательном фронте входного импульса происходит передача состояния

триггера Тг1 в триггер Тг2.

На рис. 9,б приведено символическое изображение Т-триггера.

Режим Т-триггера может быть получен с помощью JK-триггера либо

D-триггера, как показано на рис. 10,а,б.

Триггеры с

динамическим управлением.

В триггерах с динамическим управлением (управлением фронтом

синхронизирующего сигнала) процессы, связанные с переключением, происходят в

течение короткого времени вблизи фронта сигнала на синхронизирующем входе.

Синхронизирующий вход, вызывающий переключение триггера при действии

положительного сигнала, называется прямым динамическим входом (условное

обозначение прямого динамического входа триггера показано на рис. 11,а); вход,

вызывающий переключение на отрицательном фронте синхронизирующего сигнала,

называется инверсным динамическим входом (условное обозначение инверсного

динамического входа триггера приведено на рис. 11,б).

2.3.3 D-триггер

Рассмотрим функционирование D-триггера с логическом структурой,

приведенной на рис. 12,а.

Элементы И-НЕ 1 и 2 составляют простейшую выходную триггерную структуру,

состояние которой определяет состояние всего D-триггера. Элементы И-НЕ 3...6

образуют схему, формирующую сигналы Y1 и Y2, которые переключают выходную

триггерную структуру.

Запишем логические выражения, определяющие коммутирующие сигналы Y1 и Y2.

Преобразуем эти выражения, пользуясь правилом де Моргана:

( 6)

( 6)

( 7)

( 7)

Выражения построены таким образом, что переменные левых частей входят в

правые части выражений. Такие выражения имеют следующий смысл: если в правые

части подставить значения Y1 и Y2 для данного момента времени, то логические

выражения определяют для этих переменных новые значения, которые установятся в

последующие моменты времени.

При С = 0 ( = 1) Y1 = 1 Y2 = 0 и, таким образом, на входах выходной

триггерной структуры действуют пассивные уровни и в триггерной структуре сохраняется

ранее установленное в ней состояние.

= 1) Y1 = 1 Y2 = 0 и, таким образом, на входах выходной

триггерной структуры действуют пассивные уровни и в триггерной структуре сохраняется

ранее установленное в ней состояние.

Если на синхронизирующем входе С происходит переход с уровня лог, 0 к

уровню лог. 1 (т. е. воздействует фронт положительной полярности), то для

определения новых значений Y1 и Y2 в правые части выражений ( 6) и ( 7) следует

подставить значения этих переменных, соответствующие моменту времени до

поступления фронта сигнала на вход С (т. е. значения Y1 = 1 и У2 =1). При этом

Y1 =  и Y2 = D.

и Y2 = D.

Эти значения, будучи подставлены в правые части выражений ( 6) и ( 7),

приводят к тем же значениям для Y1 и Y2. Это подтверждает их устойчивость.

Активная комбинация сигналов D = 0, Y2 =0, действуя на входе элемента

И-НЕ 2, устанавливает на его выходе  = 1, на выходе элемента И-НЕ 1

устанавливается Q = 0. Триггер оказывается установленным в состояние 0. При D =

1 и Y1 = 0 активный уровень лог. 0, действуя на входе элемента И-НЕ 1,

устанавливает на его выходе Q = 1. Триггер оказывается в состоянии 1.

= 1, на выходе элемента И-НЕ 1

устанавливается Q = 0. Триггер оказывается установленным в состояние 0. При D =

1 и Y1 = 0 активный уровень лог. 0, действуя на входе элемента И-НЕ 1,

устанавливает на его выходе Q = 1. Триггер оказывается в состоянии 1.

Таким образом, при действии на входе С положительного фронта сигнала

триггер устанавливается в состояние, соответствующее поданной на вход D

информации.

Заметим, что установленные в момент фронта сигнал С уровни Y1 и Y2 в

дальнейшем в течение всего времени действия сигнала С = 1 остаются неизменными,

если даже и изменяется значение на входе D. Действительно, если подставить в

правые части выражений ( 6) и ( 7), например, комбинацию значений Y1 = 1 и Y2 =

0, то получим что и подтверждает нечувствительность значений Y1 и Y2 к

значениям сигнала на входе D после переключения триггера.

Для того чтобы могло произойти новое переключение триггера, необходимо

воздействие на входе С нового фронта положительной полярности.

Для представления триггера данного типа в схемах используется условное

изображение, показанное на рис. 12,б.

Триггеры обычно снабжают дополнительными асинхронными входами Rd

(установки в состоянии 0) и Sd (установки о состояние 1), сигналы на которых

производят установку триггеров в соответствующее состояние, независимо от

значения сигналов на входах D и С.

Цепи асинхронных входов Rd и Sd показаны на рис. 12,а штриховыми линиями.

Условное обозначение D-триггера с асинхронными входами Rd и Sd приведено на

рис. 12,в.

На рис. 13 показана схема D-триггера, построенного на элементах ИЛИ-НЕ.

Выражения для логических уровней в точках Y1 и Y2 данной схемы имеют

следующий вид (без учета входов Rd и Sd):

( 8)

( 8)

( 9)

( 9)

Анализ выражений, подобный приведенному выше применительно к триггеру,

построенному на элементах И-НЕ, показывает, что переключение триггера

происходит при отрицательном фронте сигнала на входе С. При этом переключающие

уровни определяются выражениями Y1 =  и Y2=D.

и Y2=D.

На рис. 13,б показано условное обозначение данного триггера.

2.3.4 T-триггер

Рассмотрим работу триггера, схема которого приведена на рис. 14,а.

Логические выражения для уровней на управляющих входах Y1 и Y2 (построенные

без учета показанных штриховой линией цепей установочных входов Rd и Sd):

(11)

(11)

При T = l, Y1 = Y2 = 0 входная триггерная структура сохраняет ранее

установленное о ней состояние.

Найдем для Y1 и Y2 выражения, соответствующие действию на входе Т

отрицательного фронта сигнала. Подставив в правые части выражений ( 10) и ( 11)

значения Y1 = Y2= 0, получим

Итак, при Q0 = 0 У2 = l и этим уровнем выходная триггерная структура

переключается в состояние Q = l; при Q0 = l Y1 = 1, этим уровнем выходная

триггерная структура переводится в состояние 0. Таким образом, при действии

отрицательного фронта сигнала на входе Т-триггер переключается в состояние Q,

противоположное состоянию Q0, в котором он ранее находился. Такое

функционирование соответствует таблице состояний Т-триггера (табл. 2,г).

Рассмотрим функционирование триггера со стороны установочных входов Rd и

Sd. С учетом этих входов логические выражения для Y1 и Y2 имеют следующий вид:

( (12)

( (12)

(13)

(13)

Для установки триггера в состояние Q = 0 подается сигнал Rd = l. При этом

из ( 13) Y2 = 0; из ( 12) при T = 0

Под действием таких управляющих сигналов Y1 и Y2 триггер устанавливается

в состояние Q = 0. Заметим, что после того, как будет снят сигнал со входа Rd,

остаются неизменными уровни Y1 и Y2 и они поддерживают установленное в триггере

состояние. Процессы при установке триггера в состояние 1 сигналом на входе Sd

анализируются аналогично.

2.3.5 JK-триггep

Проанализируем работу триггера, схема которого приведена на рис. 15.

Логические выражения для уровней на управляющих входах Y1 и Y2:

( (14)

( (14)

( (15)

( (15)

При C = Q на управляющих входах устанавливаются пассивные уровни Y1 = 1 и

Y2 = 1, не влияющие на состояние выходной триггерной структуры. При

положительном фронте сигнала на входе С уровни Y1 и Y2 определяются выражениями,

получаемыми из ( 14) и ( 15) при подстановке С = 1, Y1 = 1, Y2 = 1:

триггер синхронный моделирование инверсный

( 16)

( 16)

( 17)

( 17)

В табл. 3 приведены комбинации входных сигналов J, К и текущего состояния

триггера Q0, действующих в момент, непосредственно предшествующей моменту

поступления положительного фронта на вход С, а также значения Y1, Y2 и

состояния триггера Q для ближайшего момента после фронта сигнала на входе С.

Как видно из таблицы, действие сигналов J и К на состояние триггера

соответствует таблице состояний JK-триггера (табл. 2б).

Отметим следующую особенность в работе рассматриваемого триггера.

Изменение сигналов на входах J и К, происходящее после положительного фронта

сигнала на входе С, может привести к изменению состояния триггера. Как видно из

выражений ( 14) и ( 15), после действия положительного фронта сигнала на входе

С изменение сигналов J или K с уровня лог. 0 к уровню лог. 1 окажет такое же

действие, как в случае, если бы этот уровень лог. 1 был установлен на

соответствующем входе J или К перед появлением фронта на входе С.

Действительно, пусть перед поступлением фронта сигнала на входе С на

информационных входах J = 0, K = 0 и состояние триггера Q0 = 0. Очевидно, после

действия фронта состояние триггера не изменится, но если затем значение на

входе J изменится и станет J = l, то в соответствии с выражением ( 14) на управляющем

входе Y1, установится уровень Yl = 0 и триггер переключится в состояние Q = l.

Эту особенность работы рассматриваемого триггера следует учитывать при

построении цифровых устройств.

На рис. 16 приведена другая схема JK-триггера, лишенная этого недостатка.

Проанализируем работу триггера, построенного по этой схеме.

|

Таблица 3

|

|

J

|

K

|

Q0

|

Y1

|

Y2

|

Q

|

|

0

|

0

|

0

|

1

|

1

|

0

|

|

0

|

0

|

1

|

1

|

1

|

1

|

|

0

|

1

|

0

|

1

|

1

|

0

|

|

0

|

1

|

1

|

1

|

0

|

0

|

|

1

|

0

|

0

|

0

|

1

|

1

|

|

1

|

0

|

1

|

1

|

1

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

0

|

0

|

|

Таблица 4

|

|

J

|

K

|

Q0

|

Y1

|

Y2

|

Q

|

|

0

|

0

|

0

|

1

|

0

|

0

|

|

0

|

0

|

1

|

0

|

1

|

1

|

|

0

|

1

|

0

|

1

|

0

|

0

|

|

0

|

1

|

1

|

1

|

0

|

0

|

|

1

|

0

|

0

|

0

|

1

|

1

|

|

1

|

0

|

1

|

0

|

1

|

1

|

|

1

|

1

|

0

|

0

|

1

|

1

|

|

1

|

1

|

1

|

1

|

0

|

0

|

Уровни Y1 и Y2 здесь определяются следующими выражениями:

( (18)

( (18)

( (19)

( (19)

При С = 1, Y1 = 0, Y2 = 0.

Подставляя значения Y1 = Y2 = 0 в выражения ( 18) и ( 19), получаем для

момента отрицательного фронта сигнала на входе С:

( (20)

( (20)

( (21)

( (21)

Пользуясь этими выражениями, можно построить таблицу состояний триггера

после действия фронта сигнала на входе С, (табл. 4). Отсюда следует, что

функционирование триггера подчинено таблице переходов JK-триггера (табл. 2.б).

т.е, комбинация Y1 = 1; Y2 = 0 является устойчивой, и после действия на

входе С отрицательного фронта сигнала никакие изменения значений на входах J и

К не могут изменить значений управляющих сигналов Y1 и Y2. Следовательно,

триггер оказывается нечувствительным к изменению сигналов на входах J и К после

действия отрицательного фронта сигнала на входе С.

Подстановка второй комбинации значений Y1, Y2, Q в ( 18) и ( 19) приводит

к

Таким образом, и в этом состоянии триггер нечувствителен к изменению

сигналов J и К после действия на входе С отрицательного фронта сигнала

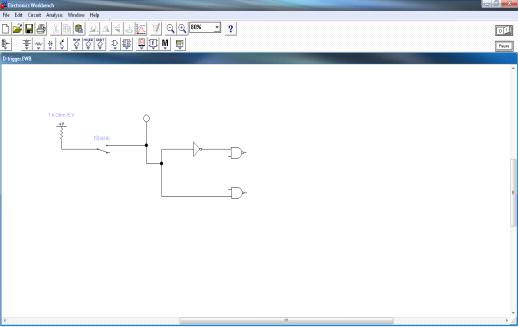

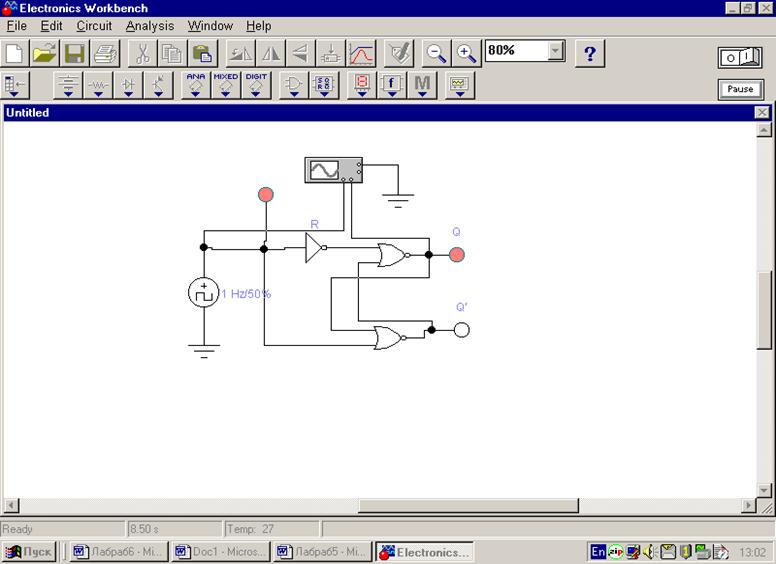

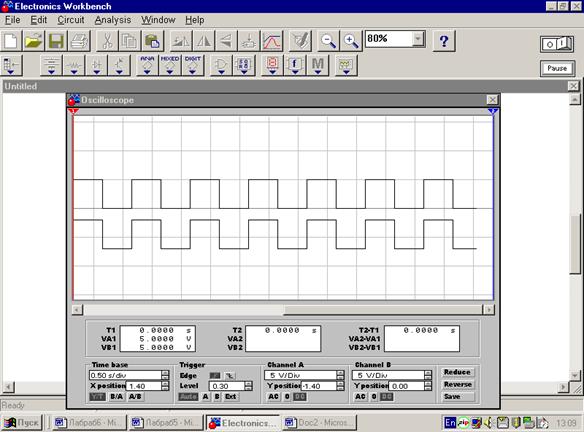

3. Математическое моделирование триггера в

приложении Electronics Workbench

В специальной части я решил исследовать D-триггер, в статическом и динамическом режимах работы, с

помощью программы Electronics Workbench.

План исследования D-триггера.

Исследование статической логики работы D-триггера

. Создание модели D-триггера

в Electronics Workbench для статического режима работы.

. Заполнение таблицы переходов для D-триггера.

Исследование динамической логики работы D-триггера

. Создание модели D-триггера

в Electronics Workbench.

. Наблюдение динамического режима работы D-триггера, при помощи осциллографа, копирование

осциллограммы.

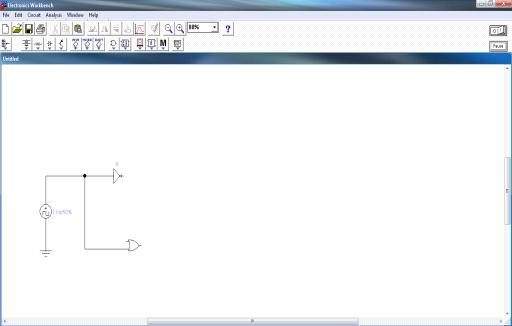

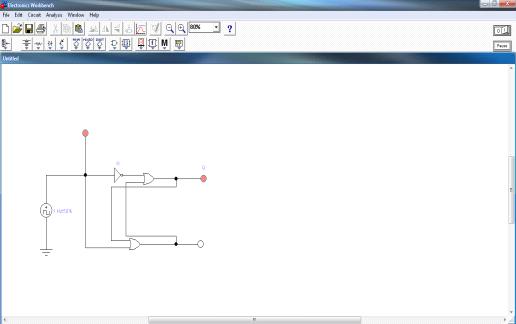

Начнем с исследования статического режима работы D-триггера, для этого я построил схему, изображенную на

следующем рисунке, используя источник тока, и индикационные лампы для

определения сигнала, и последующим занесением показаний в таблицу.

После построения схемы в приложении, основываясь на показания датчиков, я

приступил к заполнению таблицы переходов, которая представлена далее.

|

Вход

|

Состояния

|

|

D

|

Q(0)

|

Q(1)

|

|

0

|

0

|

0

|

|

1

|

1

|

1

|

Позже я сравнил показания этой таблицы с показаниями таблицы рассчитанной

ученными.

|

Вход

|

Состояния

|

|

D

|

Q(0)

|

Q(1)

|

|

0

|

0

|

0

|

|

1

|

1

|

1

|

Поскольку показатели в таблицах одинаковы, то можно сделать вывод, что

мне удалось смоделировать D-триггер

в статическом режиме работы.

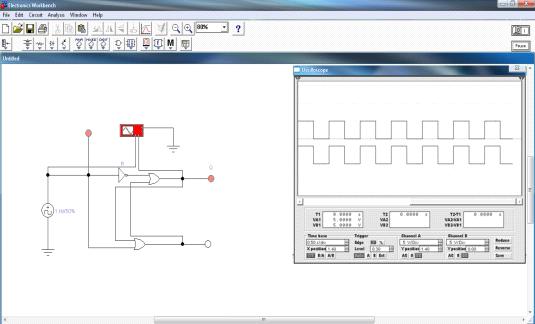

Теперь можно приступить к моделировании логики динамического режима

работы D-триггера в Electronics Workbench.

Сначала я построил D-триггер

по следующей схеме, используя осциллограф для наблюдения работы D-триггера, а также частотный

генератор с частотой в 1 Гц.

После создания D-триггера,

я снял показания осциллографа, и получил осциллограммы, что и подтверждает, то

что построенная схема способна демонстрировать динамический режим работы D-триггера, сама осциллограмма

приведена ниже.

Заключение

В ходе данной работы была максимально освещена тема триггеров, как

логических устройств, а также их типы, функционирование, и физическая

реализация.

Триггеры -это устройства предназначенные для хранения одного разряда

информации. Триггеры имеют два устойчивых состояния:

состояние "0"

состояние "1"

Триггер имеет два выхода прямой и инверсный. Состояние триггера

определяется по прямому выходу.

Типы триггеров наглядно описанных в данной работе: RS-, D-, T- и

JK-триггеры.

А также в работу указаны способы функционирования большинста типов

триггеров.

Также была раскрыта тема математического моделирования схем с

использование триггеров, что подтвердило не только возможность моделирование

логических устройств с помощью ЭВМ, но и наглядно моделировать работу данных

устройств в функциональных схемах.

Список используемой литературы

1. Новиков

Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы

проектирования. М.: Мир, 2001. - 379 с.

. Новиков

Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.:

ИНТУИТ.РУ, 2003. - 440 с.

. Пухальский

Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.:

Политехника, 2006. - 885 с.

. Букреев

И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств.

М.: Радио и связь, 2000. - 416 с.

. Соломатин

Н.М. Логические элементы ЭВМ. М.: Высш. шк., 2000. - 160 с.

7. С.Д. Кузнецов,

информационно-аналитические материалы Центра Информационных Технологий

пользованием интерфейса ядра СУБД.

8. К.Дейт. Введение в системы баз

данных. 6-е издание. «Диалектика» Киев-Москва, 1998.

9. Т.Каннолли, К.Бегг, А. Страчан -Базы

данных: проектирование, реализация и сопровождение.Теория и практика

10.КомпьютерПресс

12'2000. Copyright © КомпьютерПресс 2008

webmaster@compress.ru

11.

intuit.ru/department/hardware/archhard2/1/2.html <#"670119.files/image048.gif">

Рис. 1

На рис. 1,а. представлена логическая структура RS-триггер с прямыми

входами триггера.

На рис. 1,б приведена таблица состояний RS-триггера в форме таблицы

Вейча.

На рис. 1,в показано условное обозначение асинхронного RS-триггера.

Рис. 2

На рис.2,а приведена логическая структура RS-триггера с инверсными

входами.

На рис. 2,б показано условное обозначение RS-триггера с инверсными

входами.

Рис. 3

На рис. 3,а,б показаны логические структуры синхронного RS-триггера.

На рис. 3,в показано условное изображение синхронных RS-триггеров в

схемах.

Рис. 4

На рис. 4,а показано как функционирование D-триггера определяется

таблицей состояний.

На рис.4,б и рис.4,в представлены логические структуры D-триггера,

состоящего из асинхронного RS-триггера с логическими элементами на входах.

На рис. 4,г показано символическое изображение D-триггера.

Рис. 5

На рис. 5 показана схема с ведущим триггер и ведомы триггерами.

Рис. 6

На рис. 6 таблица состояний JK-триггера представлена в форме диаграммы

Вейча.

Рис.

7

На

рис. 7,а представлен JK-триггер с подробной логической структурой.

На

рис. 7,б приведен один из вариантов логической структуры RS-триггера.

На

рис. 7,в приведено символическое изображение JK -триггера.

Рис.

8

На

рис. 8 показано включение JK-триггера, при котором он выполняет функции

D-триггера.

Рис.

9

На

рис. 9,а показана логическая структура Т-триггера.

На

рис. 9,б приведено символическое изображение Т-триггера.

Рис.

10

На

рис. 10,а,б показано как с помощью JK-триггера либо D-триггера получить режим

Т-триггера.

Рис.

11

На

рис. 11,а показано условное обозначение

прямого динамического входа триггера.

На

рис. 11,б показано условное обозначение инверсного динамического входа

триггера.

Рис.

12

На

рис. 12, а, б ,в представлен D-триггер с логической структурой и символьными

обозначениями.

Рис.13

На рис. 13,а показана схема D-триггера, построенного на элементах ИЛИ-НЕ.

На рис.13,б показано условное обозначение данного триггера. Рис. 14

На рис. 14,а представлена схема Т- триггера.

На рис.14,б показано условное

обозначение данного триггера.

Рис. 15

На рис. 15 приведена схема JK- триггера. Рис. 16

На рис. 16 приведена схема

JK-триггера