Проектування інтелектуальних давачів на базі мікроконтролера 89С51

МІНІСТЕРСТВО

ОСВІТИ І НАУКИ УКРАЇНИ

НАЦІОНАЛЬНИЙ

УНІВЕРСИТЕТ

«ЛЬВІВСЬКА

ПОЛІТЕХНІКА»

Кафедра

АТХП

КУРСОВИЙ

ПРОЕКТ

з

курсу “мікропроцесорна техніка”

на

тему:

“ПРОЕКТУВАННЯ

ІНТЕЛЕКТУАЛЬНИХ ДАВАЧІВ НА БАЗІ МІКРОКОНТРОЛЕРА 89С51 ”

Виконав: студент групи АВ-32

Горбаль Любомир

Прийняв:

Костик І. В.

ЛЬВІВ

- 2011

Зміст

Вступ

Індивідуальне завдання

Структурна схема

інтелектуального давача, побудованого на базі мікропроцесорного пристрою

Побудова контролера клавіатури

та семисегментного індикатора

Ввід інформації з клавіатури

Вивід інформації на

восьмисегментний індикатор

Програми для програмування

програмованого логічного пристрою контролера

Часові діаграми роботи

програмованого логічного пристрою контролера

Робота аналого-цифрового

пристрою

Програма для роботи

мікропроцесорного пристрою, побудованого на базі мікроконтролера 89С51

Специфікація

Висновки

Застосована література

Вступ

На сучасному етапі

науково-технічного процесу все більше важливим стає питання впровадження у

виробничу і наукову діяльність високоточних методів ведення обрахунку, їх

фіксації і перетворення. Це пов`язане в першу чергу з підвищення вимог до

точності і надійності проведення у різних галузях науки і техніки, особливо у

вимірюваннях фізичних величин.

Використання цифрових складових у

приладах і пристроях обумовлюється в першу чергу можливістю прямого їх

використання у схемах керування, побудованих як правило на базі

мікроконтролерної техніки, що дозволяє обійтися без переходів між аналоговими і

цифровими видами представлення інформації, і відповідно зменшити похибки

результатів вимірювань.

Переваги мікроелектронних пристроїв

над аналоговими є у тому, що у них переважає висока точність вимірювання

параметрів, переважає швидкодія вимірювання та можливості використання

мікроелектронних пристроїв при непрямих вимірюваннях. При цьому основні похибки

вносять аналогові давачі, які є менш точними за цифрові

Інтелектуальні давачі переважно

застосовуються для виконання непрямих вимірювань тих величин, які неможливо

виміряти прямими методами.

Мікроконтролери серії 8х51 є восьмирозрядними

однокристальними мікро-ЕОМ, які працюють при максимальній тактовій частоті

генератора 12 МГц . Маючи восьмирозрядну внутрішню архітектуру, МК51 виконує

операції над бітами, півбайтами, байтами та машинними словами. За допомогою

непрямої адресації процесор може обробляти 16-и бітовий адрес і таким чином

адресувати 216=64 Кбайт як оперативної так і програмної пам’яті. Для виконання

операцій над бітами МК51 має булевий процесор, який є незалежним бітовим процесором

із своєю системою команд і своїм акумулятором.

Особливістю організації пам’яті

МК51

є, як фізичне, так і логічне розділення оперативної та програмної пам’яті.

Тобто оперативна пам’ять не може бути використана для зберігання програм.

Оперативна пам’ять 8х51 призначена для

зберігання і обробки даних в процесі виконання програми і ділиться на внутрішню

(вбудовану в кристал) і зовнішню (додаткові мікросхеми пам’яті). МК51 має

внутрішній оперативний запам’ятовуючий пристрій (ОЗП) об’ємом 256 байт і зовнішній

ОЗП об’ємом 64 Кбайт. В свою чергу внутрішня оперативна пам’ять складається із

128 байт пам’яті даних і 20-и регістрів спеціальних функцій.

Система команд мікроконтролера

сімейства 8х51 включає у себе 111 основних команд. Їх довжина - один, два, або

три байти, але більшість із них (94%) - це одно- або двобайтні команди. Всі

команди виконуються за один або два машинні цикли ( відповідно 1 або 2 мкс при

тактовій частоті 12 МГц ). Виключенням є команди множення та ділення, які

виконуються за чотири машинні цикли ( 4 мкс ).

Мікроконтролери сімейства 8х51 використовують

прямий, безпосередній, непрямий та неявний способи адресації даних. В якості

операндів команд мікроконтролери сімейства 8х51 можуть використовувати окремі

біти, чотирьохбітні цифри, байти або двобайтні слова. Всього мікроконтролер

виконує 13 типів команд.

Індивідуальне

завдання до курсового проекту

Варіант 5

. Розмір клавіатури: 8 x

2

. Розмірність індикатора: 8

. Параметр, який вимірюєть непрямим

методом:

поправний коефіцієнт на шорсткість

внутрішньої поверхні трубопроводу Кш

. Вхідні параметри, які

вимірюються за допомогою перетворювачів:

t = [ oC ].

. Контрольна точка: t=27 oC, d20=0.097м, D20=0.182м, Rш=2.1·10-5м, Re=7.44·105м.

7. Тип АЦП: TLC 549IP

Отримав: студент групи АВ-32:

Горбаль Л.О.

Видав: асистент кафедри АТХП:

Костик І. В.

інтеллектуальний давач

індикатор мікропроцесорний

Структурна схема інтелектуального

давача, побудованого на базі мікропроцесорного пристрою

Структурна схема інтелектуального

давача на базі мікроконтролера 89С51 наведена на рисунку 2.1 і складається з:

- мікроконтролера 89С51, який

здійснює керування зовнішніми пристроями вводу/виводу та поводить обчислення,

згідно програми по обчисленню величини Kш

(рівняння наведені в індивідуальному завданні);

- аналого-цифрового

перетворювача (АЦП TLC

549IP),

який здійснює перетворення сигналу з аналогового в цифровий ;

- клавіатури, за допомогою

якої вводяться постійні величини,

або виводяться певні величини для перевірки програми;

- восьмирозрядного

семисегментного індикатора, який потрібен для показу величин, які вводяться,

знаходяться в пам’яті (тобто вже введені), вимірюються чи обраховуються в даний

момент;

- контролер клавіатури (5С090)

та семисегментного індикатора, який обслуговує клавіатуру та семисегментний

індикатор;

контролеру каналу

послідовного вводу/виводу (ADM485),

який дозволяє обмінюватися інформацією з іншими контролерами чи з вищим рівнем

керування (наприклад комп’ютером);

блоку живлення.

Основним елементом інтелектуального давача є

мікроконтролер. Для даного проекта застосовується мікроконтролер 89С51,

загальний вигляд та призначення ніжок якого показано на рис.2.2

.

Мікроконтролер має чотири порти вводу-виводу

Р0-Р3. Порт Р0 мікроконтролера 89С51 використовується, як шина даних (коли

сигнал ALE=0) і шина адресів від А0 до А7 (коли сигнал ALE=1). Порт Р3

використовується як порт, який видає сигнали керування мікроконтролером.

Сигнали керування, які ідуть від порту Р3, наведені на рис.2.2.

Опис сигналів керування наведено в табл. 2.2.

Кожний порт може видавати сигнали керування.

Пам’ять у мікроконтролері поділяється на

внутрішню пам’ять програм та даних та зовнішню пам’ять програм да даних.

Зовнішня пам’ять програм та даних поділяється на

постійну зовнішню пам’ять програм (ПЗП), де знаходяться коди операцій, та

зовнішню пам’ять даних (ОЗП), де знаходяться проміжні результати розрахунків.

Звернення до ПЗП здійснюється за допомогою керуючого сигналу /PSEN, який

виконує функцію строб-сигналу читання. Код команди вибирається із ПЗП при

встановленні на /PSEN сигналу рівного логічному 0. Звернення (читання або

запис) до ОЗП забезпечується керуючими сигналами /RD або /WR, які формуються на

лініях Р3.7 та Р3.6 при виконанні відповідних операцій переміщення даних та

команд керування процесором. Звернення до ОЗП здійснюється при встановленні на

/RD або /WR сигналів логічного 0. Для того, щоб одночасно читати коди команд із

ПЗП та дані із ОЗП сигнали /PSEN та /RD об’єднують в один сигнал /PSEN*/RD.

Мікроконтролер 89С51 має розширену систему

переривань.Спрощена схема переривань 89С51

наведена на рис.2.3.

Зовнішні переривання /INT0 та

/INT1 можуть бути викликані або рівнем або переходом сигналу із 1 в 0 (фронтом)

на входах 89С51 в залежності від значень керуючих бітів ІТ0 та ІТ1 у регістрі

TCON. При значенні цих бітів рівних 0 сигнали зовнішніх переривань приймаються

за рівнем, а при значенні їх рівних 1 сигнали /INT0 та /INT1 сприймаються за

фронтом. Від зовнішніх переривань встановлюються прапори IE0 та IE1 у регістрі

TCON, які ініціюють виклик відповідних підпрограм обробки переривань. Скид цих

прапорів здійснюється апаратно тільки у тому випадку, якщо переривання були

викликані фронтом сигналу. Якщо ж переривання були викликані рівнем вхідного

сигналу, то скидом прапору ІЕ керує відповідна підпрограма обробки переривання

шляхом дії на джерело переривання з метою зняття ним запиту.

Прапори запитів переривань

від таймерів TF0 та TF1 скидаються автоматично при передачі керування

підпрограмі його обробки. Прапори запитів переривань RI та TI встановлюються

блоком керування універсального асинхронного приймача-передавача (УАПП)

апаратно, але скидатись повинні програмою обробки переривань.

Переривання можуть бути

викликані або відмінені програмою, так як усі перераховані прапори програмно

досягнені і можуть бути встановлені або скинуті програмою з тим же результатом,

що і якщо б вони були встановлені або кинуті апаратними засобами.

В блоці регістрів спеціальних

функцій є два регістри, які використовуються для керування режимом переривань

та рівнями їх пріоритету. Формати цих регістрів, які мають символічні імена ІЕ

та ІР, наведені у табл. 2.2 та табл. 2.3.

Обробка переривань по рівню

пріоритету виконується на протязі наступного машинного циклу. Система

переривань сформує апаратний виклик (LCALL) відповідної підпрограми обробки

переривань, якщо вона не заблокована одним із наступних умов:

) в даний момент

обслуговується переривання рівного або вищого рівня пріоритету;

) текучий машинний цикл - не

останній у циклі виконуваної команди;

) виконується команда RETI

або інша команда, яка пов’язана із зверненням до регістрів ІЕ та ІР.

Таблиця 2.1. Альтернативні

функції порта Р3.

|

P3.7Читання.

Активний сигнал низького рівня формується апаратно при зверненні до

зовнішньої пам’яті даних. P3.7Читання.

Активний сигнал низького рівня формується апаратно при зверненні до

зовнішньої пам’яті даних.

|

|

|

|

P3.6Запис.

Активний сигнал низького рівня формується апаратно при зверненні до

зовнішньої пам’яті даних. P3.6Запис.

Активний сигнал низького рівня формується апаратно при зверненні до

зовнішньої пам’яті даних.

|

|

|

|

P3.5Вхід

таймера/лічильника 1 або тест-вхід. P3.5Вхід

таймера/лічильника 1 або тест-вхід.

|

|

|

|

P3.4Вхід

таймера/лічильника 0 або тест-вхід. P3.4Вхід

таймера/лічильника 0 або тест-вхід.

|

|

|

|

P3.3Вхід

запиту переривання 1. Сприймається сигнал низького рівня або зріз по спаду

напруги. P3.3Вхід

запиту переривання 1. Сприймається сигнал низького рівня або зріз по спаду

напруги.

|

|

|

|

P3.2Вхід

запиту переривання 0. Сприймається сигнал низького рівня або зріз по спаду

напруги. P3.2Вхід

запиту переривання 0. Сприймається сигнал низького рівня або зріз по спаду

напруги.

|

|

|

|

P3.1Вихід

передавача послідовного порта. Вихід синхронізації в режимі зсуваючого

регістра. P3.1Вихід

передавача послідовного порта. Вихід синхронізації в режимі зсуваючого

регістра.

|

|

|

|

P3.0Вхід

передавача послідовного порта. Ввід/вивід даних в режимі зсуваючого регістра. P3.0Вхід

передавача послідовного порта. Ввід/вивід даних в режимі зсуваючого регістра.

|

|

|

Таблиця 2.2. Прапори дозволу

переривань

|

Джерело переривання

|

Прапор дозволу

|

Комірка біту

|

|

Зовнішній запит 0

|

EX0

|

IE.0

|

|

Внутрішній таймер / лічильник 0

|

ET0

|

IE.1

|

|

Зовнішній адрес 1

|

EX1

|

IE.2

|

|

Внутрішній таймер / Лічильник 1

|

ET1

|

IE.3

|

|

Внутрішній послідовний порт

|

ES

|

IE.4

|

|

Резервний

|

відсутній

|

IE.5

|

|

Резервний

|

відсутній

|

IE.6

|

|

Загальний дозвіл

|

EA

|

IE.7

|

Таблиця 2.3. Прапори пріоритету

переривань

|

Джерело переривання

|

Прапор пріоритету

|

Пріоритет по рівню

|

Комірка біту

|

|

Зовнішній запит 0

|

PX0

|

1(найвищий)

|

IP.0

|

|

Внутрішній таймер/лічильник 0

|

PT0

|

2

|

IP.1

|

|

Зовнішній адрес 1

|

PX1

|

3

|

IP.2

|

|

Внутрішній таймер/лічильник 1

|

PT1

|

4

|

IP.3

|

|

Внутрішній послідовний порт

|

PS

|

5(найнижчий)

|

IP.4

|

За апаратносформованим кодом LCALL

система переривань заносить у стек тільки вмістиме лічильника команд (РС) і

завантажує в лічильник команд адрес вектора відповідної підпрограми обробки. За

адресом вектору повинна бути розташована команда безумовної передачі керування

(JMP) до початкового адресу підпрограми обробки переривання. Підпрограма

обробки при необхідності повинна починатися із команд запису у стек (PUSH)

слова стану підпрограми (PSW), акумулятора, розширювача, показника даних і т.д.

та закінчуватись командами виклику зі стеку (POP) попередніх регістрів за

принципом «перший пішов останній повернувся». Підпрограми обробки переривань

повинні обов’язково закінчуватись командою RETI, за якою в лічильник команд

перенавантажується зі стеку збережений адрес повернення в основну програму.

Команда RET також повертає керування перерваній основній програмі, але при

цьому не знімають блокування переривання, що призводить до необхідності мати

програмний механізм аналізу закінчення процедури обробки переривання.

Опис роботи інтелектуального давача.

Величина, що вимірюється,

перетворюється первинним перетворювачем у аналоговий уніфікований електричний

сигнал (від 0 до 5 вольт), поступає на вхід аналого-цифрового перетворювача. На

аналого-цифровому перетворювачі аналоговий (неперервний) сигнал перетворюється

на послідовний чи паралельний цифровий код, який вже може сприймати

мікроконтролер. Далі мікроконтролер обраховує величину Z

згідно програми, та виводить результат на рідкокристалічний індикатор та, через

канал послідовного вводу/виводу, на ЕОМ.

Побудова контролера

клавіатури та семисгментного індикатора

Для обслуговування клавіатури в

мікропроцесорних системах використовується процедура вводу натиснутої клавіші.

Схема під’єднання клавіатури та індикатора до контролера клавіатури та

індикатора наведена на рисунку 3.1.

Рис 3.1. Структурна схема

під’єднання клавіатури та CCІ до

контролера

Виявлення мікропроцесорним

пристроєм натиснення клавіші на клавіатурі здійснюється за допомогою сканування

клавіатури. Детальніше процес сканування розглянемо нижче. Для побудови

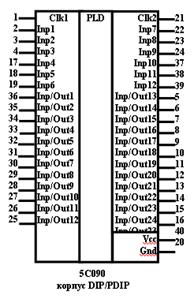

контролера індикатора та клавіатури було вибрано ПЛМ 5С090. Нумерація ніжок

серії 5С090 наведена на рисунку 3.2:

Рис 3.2. Нумерація ніжок

мікросхем серії 5С090

Ввід інформації з клавіатури

Для обслуговування клавіатури

мікропроцесорної системи використовується процедура вводу коду натиснутої

клавіші. У таблиці 3.1 показано як формується код натисненої клавіші.

Таблиця 3.1 Формування

коду натисненої клавіші

|

R0

|

R1

|

K0

|

K1

|

K2

|

K3

|

K4

|

K5

|

K6

|

K7

|

P00

|

P01

|

P02

|

P03

|

Символ

|

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

1

|

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

0

|

2

|

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

3

|

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

0

|

4

|

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

5

|

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

6

|

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

7

|

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

0

|

1

|

8

|

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

9

|

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

F

|

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

S

|

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

P

|

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

=

|

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

-

|

Лінія порту Ri використовується для

сканування, а лінія порту Ki - для опиту матриці клавіш. Значення сигналів

R0-R1 змінюються за законом зсуваючого регістру з активним вихідним нульовим

сигналом. При натисненій клавіші сигнал з лінії Ri поступає на ніжку Ki. Якщо

клавіша натиснута, то на ніжці Ri та на ніжці Кі буде активний нульовий сигнал.

Наприклад, якщо буде натиснута

клавіша F,

то нульовий сигнал буде на ніжках R1 та К5. Кожна клавіша в такій матриці має

свій номер, який відповідає її місцезнаходженню. Діоди забезпечують захист від

замикання між собою скануючих ліній у випадку одночасного натиснення більше ніж

однієї клавіші.

Для зменшення використання зовнішніх

портів мікроконтролера 89С51 контролер клавіатури та рідкокристалічного

індикатора видає на шину даних порту Р0 мікроконтролера 89С51 код заданої

клавіші. Код заданої клавіші формується контролером клавіатури та

рідкокристалічного індикатора, побудованого на програмованому логічному

пристрої типу 5С090.

Процедура вводу коду натисненої

клавіші складається із послідовності часткових процедур: сканування матриці

клавіш, усунення дребезгу контактів, очікування звільнення клавіші та

ідентифікації коду натисненої клавіші. Для деяких клавіатур може бути відсутня

процедура усунення дребезгу контактів (для клавіатури на базі герконів). Процедуру

сканування іноді об’єднують з процедурою ідентифікації.

Процедура вибору між скануванням

клавіатури та виводу інформації на CCІ

здійснюється за допомогою сигналу Р2.1. При активному нульовому сигналі

виводиться інформація на КІ, а при активному сигналі високого рівня -

сканується клавіатура

Вивід інформації на

семисегментний індикатор

Вивід інформації на

рідкокристалічний індикатор здійснюється наступним чином. Байт з порту Р0

мікроконтролера 89С51 поступає на вхід контролера клавіатури та cемисегментного

індикатора, побудованого на базі програмованого логічного пристрою 5С090.

На контролер також поступає і сигнал синхронізації CLK, який знімається з

виходу Р2.0 мікроконтролера

89С51.

При динамічній індикації байт

індикації (YА-YG) поступає від контролера одночасно на входи усіх дев’яти

семисегментних індикаторів, які утворюють лінійний дисплей, а вибір знакомісця

(R0-R8)

здійснюється бітом вибірки, який поступає зсуваючий регістра (R0-R7), що

побудований на базі програмованого логічного пристрою 5С090.

З кожним імпульсом біту вибірки

сигнал символу з порту Р0 (біти Р0.4

- Р0.7) мікроконтролера 89С51 поступає на дешифратор символів, який побудований

на тому ж програмованому логічному пристрої 5С090.

Підпрограма виводу символу на ССІ

реалізує вибірку коду наступного символу з РПД (вихідні коди символів повинні

бути розміщені у послідовно розташованих комірках пам’яті), його відображення в

текучому знакомісці. Для отримання яскравої та рівної (немигаючої) індикації

необхідно забезпечити: по-перше, заборону вибірки знакомісць на час зміни байту

індикації у порту 0 (бланкування), по-друге, регенерацію зображення на кожному

знакомісці з частотою 20 раз в секунду, тобто звертання до підпрограми через

кожні 50/9 мс, де 9 - число знакомісць на дисплеї. Бланкування здійснюється

видачею байта вибірки «всі одиниці». Відповідність

символу, що виводиться на індикатор до коду наведено у таблиці 3.2.

Таблиця 3.2. - Кодування символів

індикатора

|

P07

|

P06

|

P05

|

P04

|

YA

|

YB

|

YC

|

YD

|

YE

|

YF

|

YG

|

Символ

|

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

2

|

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

3

|

|

0

|

1

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

4

|

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

5

|

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

6

|

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

7

|

|

1

|

0

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

8

|

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

9

|

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

1

|

1

|

1

|

F

|

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

Е

|

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

S

|

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

P

|

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

=

|

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

-

|

Таблиця 3.2. Таблиця переходів та виходів роботи

контролера індикатора

|

S

|

CLK

|

Y

|

|

0

|

1

|

0

|

1

|

2

|

3

|

4

|

5

|

6

|

7

|

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

|

1

|

1

|

2

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

|

2

|

2

|

3

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

|

3

|

3

|

4

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

|

4

|

4

|

5

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

|

5

|

5

|

6

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

|

6

|

6

|

7

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

|

7

|

7

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

Програма для програмування

програмованого логічного пристрою контролера

Для програмування ПЛМ була написана

наступна програма:KURS1pds02LGNULP28.12.1991KURS1

5C090CLKIKR0R1R2R3R4R5R6R7YAYBYCYDYEYFYGQ0Q1Q2P00P01P02P03P04P05P06P07K0K1K2K3K4K5K6K7MOORE_MACHINE=/Q2*/Q1*/Q0=/Q2*/Q1*Q0=/Q2*Q1*/Q0=/Q2*Q1*Q0=Q2*/Q1*/Q0=Q2*/Q1*Q0=Q2*Q1*/Q0=Q2*Q1*Q0:=GND->S0

+VCC->S1:=GND->S1

+VCC->S2:=GND->S2

+VCC->S3:=GND->S3

+VCC->S4:=GND->S4

+VCC->S5:=GND->S5

+VCC->S6:=GND->S6

+VCC->S7:=GND->S7

+VCC->S0.OUTF=/R0*R1*R2*R3*R4*R5*R6*R7.OUTF=R0*/R1*R2*R3*R4*R5*R6*R7.OUTF=R0*R1*/R2*R3*R4*R5*R6*R7.OUTF=R0*R1*R2*/R3*R4*R5*R6*R7.OUTF=R0*R1*R2*R3*/R4*R5*R6*R7.OUTF=R0*R1*R2*R3*R4*/R5*R6*R7.OUTF=R0*R1*R2*R3*R4*R5*/R6*R7.OUTF=R0*R1*R2*R3*R4*R5*R6*/R7.CLKF=/CLK.CLKF=/CLK.CLKF=/CLK.TRST=IK.TRST=IK.TRST=IK.TRST=IK.TRST=IK.TRST=IK.TRST=IK.TRST=IK_TAB

(P07 P06 P05 P04 >> YA YB YC YD YE YF YG)

0 0 0 : 1 1 1 1 1 1 0 ;0

0 0 1 : 0 1 1 0 0 0 0 ;1

0 1 0 : 1 1 0 1 1 0 1 ;2

0 1 1 : 1 1 1 1 0 0 1 ;3

1 0 0 : 0 1 1 0 0 1 1 ;4

1 0 1 : 1 0 1 1 0 1 1 ;5

1 1 0 : 1 0 1 1 1 1 1 ;6

1 1 1 : 1 1 1 0 0 0 0 ;7

0 0 0 : 1 1 1 1 1 1 1 ;8

0 0 1 : 1 1 1 1 0 1 1 ;9

0 1 0 : 1 0 0 0 1 1 1 ;F

0 1 1 : 1 0 0 1 1 1 1 ;E

1 0 0 : 1 0 1 1 0 1 1 ;S

1 0 1 : 1 1 0 0 1 1 1 ;P

1 1 0 : 0 0 0 1 0 0 1 ;=

1 1 1 : 0 0 0 0 0 0 1 ;-_TAB (R0 R1

K0 K1 K2 K3 K4 K5 K6 K7 >> P03 P02 P01 P00)

0 0 1 1 1 1 1 1 1: 0 0 0 0 ;0

1 0 1 1 1 1 1 1 1: 0 0 0 1 ;1

0 1 0 1 1 1 1 1 1: 0 0 1 0 ;2

1 1 0 1 1 1 1 1 1: 0 0 1 1 ;3

0 1 1 0 1 1 1 1 1: 0 1 0 0 ;4

1 1 1 0 1 1 1 1 1: 0 1 0 1 ;5

0 1 1 1 0 1 1 1 1: 0 1 1 0 ;6

1 1 1 1 0 1 1 1 1: 0 1 1 1 ;7

0 1 1 1 1 0 1 1 1: 1 0 0 0 ;8

1 1 1 0 1 0 1 1 1: 1 0 0 1 ;9

0 1 1 1 1 1 0 1 1: 1 0 1 0 ;F

1 1 1 1 1 1 0 1 1: 1 0 1 1 ;-

0 1 1 1 1 1 1 0 1: 1 1 0 0 ;F

1 1 1 1 1 1 1 0 1: 1 1 0 1 ;R

0 1 1 1 1 1 1 1 0: 1 1 1 0 ;B

1 1 1 1 1 1 1 1 0: 1 1 1 1

;BINPI:=[P07 P06 P05 P04]OUTK:=[P00 P01 P02 P03]S:=[Q2 Q1 Q0]/IKI:=0 TO 15

DOINPI:=IIK CLKQ2 Q1 Q0I:=0 TO 8 DOK0 K1 K2 K3 K4 K5 K6 K7I=0 THEN/K0I=1

THEN/K1I=2 THEN/K2I=3 THEN/K3I=4 THEN/K4I=5 THEN/K5I=4 THEN/K6I=5 THEN/K7CLK

С090

Gnd

- | 1 21 | - Vcc

K7

- | 2 22 | - P04

K6

- | 3 23 | - P05

K5

- | 4 24 | - P06

Q0

- | 5 25 | - IK

Q2

- | 6 26 | - CLK

Q1

- | 7 27 | - YG

R0

- | 8 28 | - P00

R1

- | 9 29 | - P01

YF

- | 10 30 | - P02

YE

- | 11 31 | - P03

YD

- | 12 32 | - R2

YC

- | 1 33 | - R3

YB

- | 14 34 | - R4

YA

- | 15 35 | - R5

R7

- | 16 36 | - R6

K4

- | 17 37 | - P07

K3

- | 18 38 | - K0

K2

- | 19 39 | - K1

GND

- | 20 40 | - Gnd

Рис 3.3. Призначення ніжок

контролера клавіатури та індикатора

Часові діаграми доботи

програмованого логічного пристрою контролера.

Рис 3.4 Часова діаграма роботи

клавіатури

Рис 3.5 Часова діаграма роботи

регістру зсуву.

Рис. 3.6 Часова діаграма виводу

символів на ССІ.

Робота

аналого-цифрового перетворювача

На сьогоднішній день випускають

аналого-цифрові перетворювачі (АЦП) в корпусах з вісьма ніжками. Вони

використовуються для роботи з сучасними компонентами - RISC-мікроконтролерами

та цифровими сигнальними процесорами (ЦСП).

Головна особливість таких АЦП

полягає в організації керування на одно- або двопровідній шині (SPI, Microwire,

I2C та інших), а не через паралельний канал вводу-виводу, який вимагає

наявності одного виводу мікросхеми на кожний розряд шини керування. Звичайно,

такий спосіб передачі бітів даних - один за одним по одному проводу - обмежує

швидкість обміну інформацією, хоча і тут можна досягти швидкості передачі даних

1Мбіт/с.

На рис.4.1 наведена структурна схема

стандартного послідовного АЦП, виконаних в корпусах з 8 ніжками. Логічний

контролер з вбудованим тактовим генератором керує роботою схеми перетворення,

яка функціонує за принципом послідовного наближення. Цей принцип полягає у

покроковому накопиченні в проміжному регістрі даних двійкового слова, яке

відповідає співвідношенню вхідної аналогової напруги та взірцевої напруги

(REF).

Розглянемо застосування ніжок

мікросхеми MAX1242.

Такий АЦП має один аналоговий вхід

АIN та вхід для підключення взірцевої напруги (REF). На виході АЦП буде

формуватись байт вихідного коду, який рівний 000000000000 для нульової напруги

на аналоговому вході, та 111111111111 - для вхідної напруги, яка рівна опорній,

що подається на вхід REF. На вхід АIN

повинна

подаватися напруга менша 2.5 вольта.

Рисунок 4.1. Структурна схема

послідовного АЦП.

549IP

Кожний біт вихідних даних

зчитується на ніжці Sdata, при чому біти виводяться старшими розрядами (MSB)

вперед за переднім фронтом імпульсів на ніжці SCLK.

Протокол зв’язку АЦП TLC 549IP

наведений на рисунку 4.2

Таблиця 4.1 - Призначення

ніжок для мікросхем фірм Linear Technology.

|

Назва ніжки

|

Призначення ніжки

|

|

Sdata

|

послідовний цифровий вихід

|

|

REF

|

вхід взірцевої напруги

|

|

SCLK

|

тактований вхід

|

|

/CS

|

вибір кристалу

|

|

АIN

|

аналоговий вхід

|

|

VCC

|

Напруга живлення

|

|

GND

|

Загальний

|

Схема підключення АЦП до

мікроконтролера

Програма для роботи

мікропроцесорного пристрою, побудованого на базі мікроконтролера 89С51

Нижче приведена, написана мовою

асемблера 89С51, програма виконує обрахунки за заданими залежностями, а саме:

У наступній таблиці наведено

позначення змінних, їх адреси, а також їх значення у форматі, з яким працює

89С51 з десяткової системи числення значення переводилися за допомогою програми

М51-24:

|

Змінна

або число

|

Значення

|

Позначення

|

Адрес

байту

|

Значення

байту

|

27TM1H

27TM1H

H

H

H58 H

H

H

0.097DM20M1M2M3P34

H

0.097DM20M1M2M3P34

H

H

H

H46 HHH

0.182DV20M1M2M3P38

H

0.182DV20M1M2M3P38

H

H

A H

B H3A H

E H

H

2.1·15-5RSM1C H

2.1·15-5RSM1C H

D H

E H

F H30 H

H

H

7.44·105REM1H

7.44·105REM1H

H

H

H35 HH

H

-ATSUM1H

-ATSUM1H

H

H

H-

-DMM1H

-DMM1H

H

A H

B H-

-ATDM1C H

-ATDM1C H

D H

E H

F H-

-DVM1H

-DVM1H

H

H

H-

-MM1H

-MM1H

H

H

H-

-ASM1H

-ASM1H

H

A H

B H-

-R0M1M2M3P5C H

-R0M1M2M3P5C H

D H

E H

F H-

-AREM1H

-AREM1H

H

H

H-

-KSM1H

-KSM1H

H

A H

B H-

|

-

|

|

|

|

|

|

Y

|

-

|

YM1 YM2 YM3 YP

|

7C H 7D H 7E H 7F H

|

- - - -

|

|

X

|

|

XM1 XM2 XM3 XP

|

80 H 81 H 82 H 83 H

|

- - - -

|

|

XX

|

-

|

XXM1 XXM2 XXM3 XXP

|

84 H 85 H 86 H 87 H

|

- - - -

|

|

-

|

10-6

|

- - - -

|

- - - -

|

06 H 37 H BD H 6D H

|

|

-

|

9.903

|

- - - -

|

- - - -

|

1E H 72 H B0 H 84 H

|

|

-

|

20.561

|

- - - -

|

- - - -

|

24 H 7C H ED H 85 H

|

|

-

|

10-3

|

- - - -

|

- - - -

|

03 H 12 H 6E H 77 H

|

|

-

|

-15.675

|

- - - -

|

- - - -

|

FA H CC H CC H 84 H

|

|

-

|

1

|

- - - -

|

- - - -

|

00 H 00 H 00 H 81 H

|

|

-

|

-20

|

- - - -

|

- - - -

|

A0 H 00 H 00 H 85 H

|

|

-

|

11.1

|

- - - -

|

- - - -

|

31 H 99 H 99 H 84 H

|

|

-

|

7.9

|

- - - -

|

- - - -

|

7C H CC H CC H 83 H

|

|

-

|

-3.9

|

- - - -

|

- - - -

|

F9 H 99 H 99 H 82 H

|

|

-

|

104

|

- - - -

|

- - - -

|

1C H 40 H 00 H 8E H

|

|

-

|

0.045

|

- - - -

|

- - - -

|

38 H 51 H EB H 7C H

|

|

-

|

-0.025

|

- - - -

|

- - - -

|

CC H CC H CC H 7B H

|

|

-

|

-6

|

- - - -

|

- - - -

|

C0 H 00 H 00 H 83 H

|

|

-

|

-4

|

- - - -

|

- - - -

|

80 H 00 H 00 H 83 H

|

|

-

|

106

|

- - - -

|

- - - -

|

74 H 24 H 00 H 94 H

|

Програма розрахунку заданої функції

TM1

EQU 30h

TM2

EQU 31h

TM3

EQU 32h

TP

EQU 33h

DM20M1

EQU 34h

DM20M2

EQU 35h

DM20M3

EQU 36h

DM20P

EQU 37h

DV20M1

EQU 38h

DV20M2

EQU 39h

DV20M3

EQU 3Ah

DV20P

EQU 3Bh

RSM1

EQU 3Ch

RSM2

EQU 3Dh

RSM3

EQU 3Eh

RSP

EQU 3Fh

REM1

EQU 40h

REM2

EQU 41h

REM3

EQU 42h

REP

EQU 43h

ATSUM1

EQU 44h

ATSUM2

EQU 45h

ATSUM3

EQU 46h

ATSUP

EQU 47h

DMM1

EQU 48h

DMM2

EQU 49h

DMM3

EQU 4Ah

DMP

EQU 4Bh

ATDM1

EQU 4Ch

ATDM2

EQU 4Dh

ATDM3

EQU 4Eh

ATDP

EQU 4Fh

DVM1

EQU 50h

DVM3

EQU 52h

DVP

EQU 53h

MM1

EQU 54h

MM2

EQU 55h

MM3

EQU 56h

MP

EQU 57h

ASM1

EQU 58h

ASM2

EQU 59h

ASM3

EQU 5Ah

ASP

EQU 5Bh

R0M1

EQU 5Ch

R0M2

EQU 5Dh

R0M3

EQU 5Eh

R0P

EQU 5Fh

AREM1

EQU 74h

AREM2

EQU 75h

AREM3

EQU 76h

AREP

EQU 77h

KSM1

EQU 78h

KSM2

EQU 79h

KSM3

EQU 7Ah

KSP

EQU 7Bh

YM1

EQU 7Ch

YM2

EQU 7Dh

YM3

EQU 7Eh

YP

EQU 7Fh

XM1

EQU 80h

XM2

EQU 81h

XM3

EQU 82h

XP

EQU 83h

XXM1

EQU 84h

XXM2

EQU 85h

XXM3

EQU 86h

XXP

EQU 87h

STEK

EQU 70h

ORG

0h

JMP

BEGIN

ORG

100h

BEGIN

MOV

SP,#STEK

MOV

TM1,#58h

MOV

TM2,#00h

MOV

TM3,#00h

MOV

TP,#85h

MOV

DM20M1,#46h

MOV

DM20M2,#0A7h

MOV

DM20M3,#0EFh

MOV

DM20P,#7Dh

MOV

DV20M1,#3Ah

MOV

DV20M2,#5Eh

MOV

DV20M3,#35h

MOV

DV20P,#7Eh

MOV

RSM1,#30h

MOV

RSM2,#29h

MOV

RSM3,#28h

MOV

RSP,#71h

MOV

REM1,#35h

MOV

REM2,#0A4h

MOV

REM3,#00h

MOV

REP,#94h

MOV

R0,TM1

MOV

R1,TM2

MOV

R2,TM3

MOV

R3,TP

MOV

R4,#03h

MOV

R5,#12h

MOV

R6,#6Eh

MOV

R7,#77h

CALL

MUL;y=t*e-3YM1,R0YM2,R1YM3,R2YP,R3XM1,R0XM2,R1XM3,R2XP,R3R0,XM1R1,XM2R2,XM3R3,XPMUL;(t*e-3)^2R4,#0FAhR5,#0CChR6,#0CChR7,#84hMUL;x=-15.675*(t*e-3)^2XM1,R0XM2,R1XM3,R2XP,R3R0,YM1R1,YM2R2,YM3R3,YPR4,#24hR5,#7ChR6,#0EDhR7,#85hMUL;20.561*(t*e-3)R4,XM1R5,XM2R6,XM3R7,XPSUM;x+20.561*(t*e-3)R4,#1EhR5,#72hR6,#0B0hR7,#84hSUM;9.903+x+20.561*(t*e-3)R4,#06hR5,#37hR6,#0BDhR7,#6DhMUL;atsu=1e-6*(9.903+x+20.561*(t*e-3))ATSUM1,R0ATSUM2,R1ATSUM3,R2ATSUP,R3R0,TM1R1,TM2R2,TM3R3,TPR4,#0A0hR5,#00hR6,#00hR7,#85hSUM;t-20R4,ATSUM1R5,ATSUM2R6,ATSUM3R7,ATSUPMUL;atsu*(t-20)R4,#00hR5,#00hR6,#00hR7,#81hSUM;1+atsu*(t-20)R4,DM20M1R5,DM20M2R6,DM20M3R7,DM20PMUL;d=d20*(1+atsu*(t-20)DMM1,R0DMM2,R1DMM3,R2DMP,R3R0,YM1R1,YM2R2,YM3R3,YPR4,YM1R5,YM2R6,YM3R7,YPMUL;(t*e-3)^2R4,#0F9hR5,#99hR6,#99hR7,#82hMUL;xx=-3.9*(t*e-3)^2XXM1,R0XXM2,R1XXM3,R2XXP,R3R0,YM1R1,YM2R2,YM3R3,YPR4,#7ChR5,#0CChR6,#0CChR7,#83hMUL;7.9*(t*e-3)R4,XXM1R5,XXM2R6,XXM3R7,XXPSUM;7.9*(t*e-3)-3.9*(t*e-3)^2R4,#31hR5,#99hR6,#99hR7,#84hSUM;11.1+7.9*(t*e-3)-3.9*(t*e-3)^2R4,#06hR5,#37hR6,#0BDhR7,#6DhMUL;atd=1e-6(11.1+7.9*(t*e-3)-3.9*(t*e-3)^2)ATDM1,R0ATDM2,R1ATDM3,R2ATDP,R3R0,TM1R1,TM2R2,TM3R3,TPR4,#0A0hR5,#00hR6,#00hR7,#85hSUM;t-20R4,ATDM1R5,ATDM2R6,ATDM3R7,ATDPMUL;atsu*(t-20)R4,#00hR5,#00hR6,#00hR7,#81hSUM;1+atsu*(t-20)R4,DV20M1R5,DV20M2R6,DV20M3R7,DV20PMUL;D=D20*(1+atsu*(t-20))DVM1,R0DVM2,R1DVM3,R2DVP,R3R0,DMM1R1,DMM2R2,DMM3R3,DMPR4,DVM1R5,DVM2R6,DVM3R7,DVPDIV;d/DXM1,R0XM2,R1XM3,R2XP,R3R4,XM1R5,XM2R6,XM3R7,XPMUL;m=(d/D)^2MM1,R0MM2,R1MM3,R2MP,R3R0,RSM1R1,RSM2R2,RSM3R3,RSPR4,DVM1R5,DVM2R6,DVM3R7,DVPDIV;Rs/DR4,#1ChR5,#40hR6,#00hR7,#8EhMUL;as=1e4*Rs/DASM1,R0ASM2,R1ASM3,R2ASP,R3R0,ASM1R1,ASM2R2,ASM3R3,ASPLN;ln(as)R4,#38hR5,#51hR6,#0EBhR7,#7ChMUL;0.045*ln(as)R4,#0CChR5,#0CChR6,#0CChR7,#7BhSUM;r0=0.045*ln(as)-0.025R0M1,R0R0M2,R1R0M3,R2R0P,R3R0,REM1R1,REM2R2,REM3R3,REPR4,#74hR5,#24hR6,#00hR7,#94hSUMACC.7,FORMULAAREM1,#00hAREM2,#00hAREM3,#00hAREP,#81hENDA:R0,REM1R1,REM2R2,REM3R3,REPLN;ln(Re)R4,#0C0hR5,#00hR6,#00hR7,#83hSUM;ln(Re)-6XM1,R0XM2,R1XM3,R2XP,R3R4,XM1R5,XM2R6,XM3R7,XPMUL;(ln(Re)-6)^2R4,#80hR5,#00hR6,#00hR7,#83hDIV;((ln(Re)-6)^2)/(-4)R4,#00hR5,#00hR6,#00hR7,#81hSUM;are=1+((ln(Re)-6)^2)/(-4)AREM1,R0AREM2,R1AREM3,R2AREP,R3:R0,MM1R1,MM2R2,MM3R3,MPR4,MM1R5,MM2R6,MM3R7,MPMUL;m^2R4,AREM1R5,AREM2R6,AREM3R7,AREPMUL;are*m^2R4,R0M1R5,R0M2R6,R0M3R7,R0PMUL;r0*are*m^2R4,#00hR5,#00hR6,#00hR7,#81hSUM;1+r0*are*m^2KSM1,R0KSM2,R1KSM3,R2KSP,R3

В результаті виконання програми

отримаємо значення функції 1.0196.

Для перевірки правильності роботи

програми, складено програму в Matlab:

%rozrahunok;clear=27;d20=0.097;D20=0.182;Rs=2.1e-5;Re=7.44e5;=1e-6*(9.903+20.561*(t/1e3)-15.675*(t/1e3)^2);=d20*(1+atsy*(t-20));=1e-6*(11.1+7.9*(t/1e3)-3.9*(t/1e3)^2);=D20*(1+atD*(t-20));=(d/D)^2;=1e4*Rs/D;=0.045*log(As)-0.025;Re<1e6=1-(log(Re)-6)^2/4;=1;=1+r0*m^2*Are

Результати виконання програми:

.0197

Відносна обчислення мікроконтролером складає:

Висновки

У цьому курсовому проекті

було розроблено інтелектуальний давач на базі мікроконтролера 89С51.

Також розроблено:

Структурну схему

інтелектуального давача, побудованого на базі мікропроцесорного пристрою, яка в

свою чергу складається з:

мікроконтролера 89С51, який

здійснює керування зовнішніми пристроями вводу/виводу;

аналого-цифрового

перетворювача (АЦП TLC 549IP);

клавіатури;

восьмирозрядного

семисегментного індикатора;

контролера клавіатури;

контролера каналу

послідовного вводу/виводу;

блоку живлення;

Роботу контролера клавіатури

та РКІ

синтезовано

в середовищі PLDshell в

пункті 3. Результат наведений в п.3.3. та в п.3.4.

Розроблено також електричну

схему інтелектуального давача.

Описано принцип

роботи клавіатури разом з контролером клавіатури.

Описано принцип роботи семисегментного

індикатора разом з контролером індикатора.

Написано програму

для програмування програмованого логічного пристрою, який буде

обслуговувати клавіатуру та семисегментний індикатор.

Наведено часові

діаграми роботи програмованого логічного пристрою для перевірки всіх етапів

синтезу контролера.

Написано програму

для обслуговування конкретного переривання та для розрахунку функції, заданої в

індивідуальному завданні.

Результат виконання програми

на асемблері: Кш

= 1.0196

Результат виконання програми в

середовищі

Matlab: Кш = 1.0197

Вищенаведена програма

обраховує залежність з точністю

Список літератури

1.

Цифрова техніка: Навчальний посібник /Б.Є. Рицар. - Київ: УМК ВО, 1991. - 372с.

2.

Жабин В.И., Ткаченко В.В. Однокристальные и микропрограммируемые ЭВМ. - Киев,

1995, 115 с.

.

Стрепко І.Т., Тимченко О.В., Дурняк Б.В. Проектування систем на однокристальних

мікро-ЕОМю - К.: Фенікс, 1998. -266с.