|

|

|

|

|

|

|

|

|

00

|

01

|

11

|

10

|

|

|

00

|

0

|

1

|

0

|

1

|

|

|

01

|

0

|

0

|

0

|

0

|

|

|

11

|

0

|

0

|

0

|

0

|

|

|

10

|

1

|

1

|

0

|

1

|

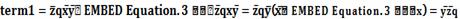

Операцию склеивания также можно представить в

такой форме:

|

term1)

|

x

|

y

|

q

|

|

0

|

0

|

0

|

1

|

|

1

|

0

|

0

|

1

|

|

|

|

|

|

|

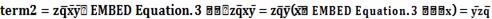

term2)

|

x

|

y

|

z

|

q

|

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

|

|

|

|

|

|

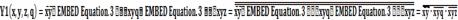

term3)

|

x

|

y

|

z

|

q

|

|

1

|

0

|

0

|

0

|

|

1

|

0

|

1

|

0

|

|

|

|

|

|

|

|

|

|

|

|

|

В итоге, МДНФ функции Y2:

Представим функции Y1 и Y2 в базисе «И-НЕ».

Перевод в заданный базис проводится с

использованием правила де Моргана и закона двойного отрицания.

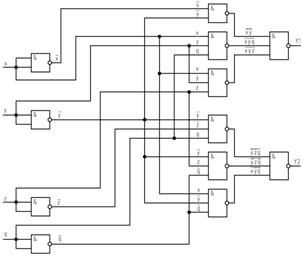

4. Функциональная логическая схема

минимизированных функций алгебр логики Y1 и Y2

Рис. 2

5. Выбор технического решения.

Обоснование

Из рис.2 видно, что в схеме содержится 7

элементов 3И-НЕ и 5 элементов 2И-НЕ.

Выбор интегральной микросхемы.

Для реализации логических функций схемы рис.2

используем интегральные микросхемы из 155 серии ТТЛ (SN74): К155ЛА3 (или

К155ЛА13), состоящая из четырех логических элементов 2И-НЕ и К155ЛА4 (или

К155ЛА10), состоящая из трех логических элементов 3И-НЕ.

Типовые параметры микросхем серии К155:

. Время задержки распространения - 10нс;

. Удельная потребляемая мощность - 10мВт/лэ;

. Работа переключения - 100пДж;

. Коэффициент разветвления по выходу - 10;

. Напряжение питания - +5В;

. Выпускается в пластмассовых корпусах с

вертикальным расположением выводов типа DIP;

. Отклонение напряжения питания от номинального

значения: ±5%;

. Диапазон рабочих температур - -10…+700С;

Предельно допустимые значения параметров и

режимов эксплуатации микросхем серии К155 в диапазоне рабочих температур:

. Кратковременное, в течении 5нс, напряжение

питания - 7В;

. Максимальное постоянное напряжение питания -

5,25В;

. Минимальное постоянное напряжение питания -

4,75В;

. Максимальное напряжение между входами - 5,5В;

. Минимальное отрицательное напряжение на входе

- -0,4В;

. Максимальное напряжение логического «0» на

входе - 0,8В;

. Минимальное напряжение логической «1» на входе

- 2,0В;

. Максимальное напряжение на запертом выходе -

5,25В;

. Максимальный выходной ток логического «0» -

16мА;

. Максимальный выходной ток логической «1» -

1-0,4мА;

. Максимальная емкость нагрузки - 15пФ;

Конструктивные параметры микросхем серии К155

(чертеж в масштабе М1:2)

Рис. 3

Выберем из микросхем К155ЛА4 и К155ЛА10 наиболее

оптимальный вариант по их параметрам.

|

Параметры

при +25ºС

|

К155ЛА4

|

К155ЛА10

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Здесь,

- ток потребления

при низком уровне напряжения;

- ток потребления

при низком уровне напряжения;

- ток потребления

при высоком уровне напряжения;

- ток потребления

при высоком уровне напряжения;

- выходной ток

низкого уровня;

- выходной ток

низкого уровня;

- входной ток

низкого уровня;

- входной ток

низкого уровня;

- входной ток

высокого уровня;

- входной ток

высокого уровня;

- выходное

напряжение низкого уровня;

- выходное

напряжение низкого уровня;

- выходное

напряжение высокого уровня;

- выходное

напряжение высокого уровня;

задержка распространения отрицательного

выходного сигнала

относительно входного

относительно входного

.

.

задержка распространения положительного

выходного сигнала относительно входного;

потребляемая статическая мощность на один

элемент.

Из характеристик интегральных микросхем К155ЛА4

и К155ЛА10 видно, что микросхема К155ЛА4 отличается от К155ЛА10 только

параметром. У микросхемы К155ЛА4 он меньше. А если мал, то выходной импульс

запоздает мало и среднее время задержки распространения сигнала сократится, что

увеличивает эффективность интегральной микросхемы.

Следовательно, выбираем микросхему К155ЛА4

(аналог 7410PC).

Выберем из микросхем К155ЛА3 и К155ЛА13 наиболее

оптимальный вариант по их параметрам.

|

Параметры

при +25ºС

|

К155ЛА3

|

К155ЛА13

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Анализируя характеристики интегральных микросхем

К155ЛА3 и К155ЛА13 выбираем микросхему К155ЛА3 (аналог 7400PC)., т.к. у нее

параметры  и меньше чем у

К155ЛА13.

и меньше чем у

К155ЛА13.

Т.о. выбираем микросхемы К155ЛА3 и К155ЛА4:

Рис. 4

|

№

выв.

|

Назначение

|

|

1

|

Вход

|

|

2

|

Вход

|

|

3

|

Выход

|

|

4

|

Вход

|

|

5

|

Вход

|

|

6

|

Выход

|

|

7

|

Общий

GDN (-5В)

|

|

8

|

Выход

|

|

9

|

Вход

|

|

10

|

Вход

|

|

11

|

Выход

|

|

12

|

Вход

|

|

13

|

Вход

|

|

14

|

(+5В) (+5В)

|

Принципиальная схема цифрового автомата.

Для составления принципиальной и монтажной схем,

нам необходимо определить количество микросхем, а также, дополнительного

оборудования, поэтому составляем спецификации используемых микросхем и

оборудования (табл.3, табл.4).

Таблица 3 - Спецификация используемых микросхем

|

№

п/п

|

Тип

микросхемы

|

Кол-во

|

Обозначение

в схеме

|

Примечание

|

|

1

|

К155ЛА4

|

3

|

D1,

D2, D3

|

|

|

2

|

К155ЛА3

|

1

|

D4

|

|

Таблица - Спецификация дополнительного

оборудования

|

№

п/п

|

Тип

оборудования

|

Кол-во

|

Обозначение

в схеме

|

Примечание

|

|

1

|

Коннектор

CONN-SIL2

|

2

|

XS2,

XS3

|

|

|

2

|

Коннектор

CONN-SIL4

|

1

|

XS1

|

|

Микросхемы D1, D2 и элемент D3.1 микросхемы D3,

работают в режиме 3И-НЕ.

Элемент D3.2 микросхемы D3, работает в режиме

2И-НЕ. Для этого в элементе соединим ножки 4 и 5.

Микросхема D4 работает в режиме 2И-НЕ.

Рис. 5

Монтажная схема представлена в масштабе М1:2.

Тип монтажа и размещения элементов: печатная плата.

Трассировка дорожек печатной платы:

двухсторонняя (трассировка дорожек печатной платы выполнена в программном

комплексе Proteus v7.7).

Геометрические характеристики монтажа:

толщина платы: 1,25мм;

высота зазора (верх): 10мм;

высота зазора (низ): 1мм;

Выводы

Расчетно-графическая работа была выполнена по

дисциплине "Основы электроники" по теме "Синтез и исследование

логической схемы цифрового автомата, построенного на цифровых

микросхемах".

В расчетно-графической работе была разработана

схема цифрового автомата, принцип работы которого был определен функциями

алгебр логики Y1 и Y2. По таблице истинности и данным логическим функциям Y1 и

Y2, была составлена СДНФ логических функций, которые, с помощью карт Карно,

минимизировали в МДНФ и представили в базисе И-НЕ.

С помощью МДНФ была построена функциональная

схема цифрового автомата, которая использовалась для создания принципиальной

схемы ЦА.

Принципиальная схема цифрового автомата

построена с использованием микросхем серии К155 имеющей достаточно высокое

быстродействие. Схема построена на логических элементах базиса И-НЕ. Общее

количество микросхем 4, потребляемая мощность 39,4 мВт. По принципиальной схеме

была составлена монтажная схема печатной платы с размещением элементов и

трассировкой дорожек.

Список используемой литературы

1. Безуглов

Д.А., Калиенко И.В. Цифровые устройства и микропроцессоры. Учебное пособие. 2-е

издание. Р-Д., 2008. - 469 с.

2. Джон

Ф. Уэйкерли. Проектирование цифровых устройств. Т.1.М.: Постмаркет, 2002. - 533

с.

. Бойко

В.И. Схемотехника электронных систем. Цифровые устройства. С-П.: БХВ-Петербург,

2004. - 501 с.

. Миловзоров

В.П. Элементы информационных систем.М.: Высшая школа, 1989. - 434 с.

. Новиков

Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы

проектирования. М.: Мир, 2001. - 379 с.

. Новиков

Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.:

ИНТУИТ.РУ, 2003. - 440 с.

. Сапожников

Н.Е. Основы программирования и вычислительной техники. - Ч. 1 / Н.Е.

Сапожников. - Севастополь: СИЯЭиП, 1990. - 200 с.

. Шило

В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1988. - 352 с.

. Усатенко

С.Т. Выполнение электрических схем по ЕСКД: Справочник / С.Т. Усатенко и др. -

М.: Изд-во стандартов, 1989. - 325 с.

. Основы

устройства и применения вычислительной техники / Под ред. В.Я. Суханова. -

Петродворец: ВВМУРЭ им. А.С. Попова, 1987. - 600 с.

. Пухальский

Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.:

Политехника, 2006. - 885 с.

. Преснухин

Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.:

Высш. шк., 2001. - 526 с.

. Букреев

И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств.

М.: Радио и связь, 2000. - 416 с.